# 行政院國家科學委員會專題研究計畫 成果報告

# 先進製程下的可繞性及效能導向 SOC 繞線系統的開發(I)

計畫類別: 個別型計畫

計畫編號: NSC92-2218-E-216-001-

執行期間: 92年08月01日至93年07月31日

執行單位: 中華大學資訊工程學系

計畫主持人:顏金泰

計畫參與人員: 陳彥翔 李佳芳 陳逢銘

報告類型: 精簡報告

處理方式: 本計畫可公開查詢

中 華 民 國 93 年 12 月 6 日

# 先進製成下的可繞性及效能導向 SOC 繞線系統的開發(I) Development of Routability-and-Performance-Driven SOC Routing System in Advanced Process Environment(I)

計畫編號: NSC 92-2218-E-216-001

執行期限:92年8月1日至93年7月31日

主持人:顏金泰 中華大學資訊工程學系

計畫參與人員:陳彥翔 李佳芳 陳逢銘 中華大學資訊工程學系

# 一、中英文摘要

基本上,傳統製程只提供少量金屬層,因此已擺置之區塊的上方無法提供金屬層作為繞線之用,對於已擺置之區塊的 繞線程序需要擴充區塊間的空間來完成, 因而形成所謂通道為基礎的繞線模式。隨 著新世代製程能提供較多的金屬層,已擺 置之區塊上方的金屬層已能作為繞線程 用,不需擴充區塊間的空間來完成繞線程 序,這樣的繞線型式稱為無通道繞 線模式。既然對於複雜 SOC 晶片的實現需 要仰賴新世代製程的應用,因此發展無通 道繞線系統對於 SOC 晶片整合是相當重 要的。

此計劃希望針對新世代製程環境的高效能與可繞性需求做整合性全晶片繞線的研究,整個繞線系統大致分為高效能導向的總體繞線與有效解決可繞性需求的全晶片細部繞線等兩個主要部份。本年計畫提出有效率新的高效能總體繞線的方法,這樣的研究盼望對於新世代製程環境中高運算頻率 SOC 晶片的開發提出有效的解決方法,也對於超大型積體電路設計自動化軟體工具的開發提供有價值的貢獻。

**關鍵詞**:先進製程,系統晶片,緩衝器插入,線寬設定

#### Abstract

Basically, traditional process only has fewer metal layers, and no metal layer over the placed blocks can be used for the routing phase. The wire connections among the blocks are routed in the extended space between any pair of adjacent blocks. Hence, the routing model is called as channel-based routing model. Now, a new advanced process has more metal layers, and the metal layers over the placed blocks can be used for the routing phase. The wire connections among the blocks are routed in the metal layers over the placed blocks. Hence, the routing model is called as channelless routing model. Since the implementation of a complex SOC chip depends on the application of a new advanced process, it is important for the integration of a SOC chip to develop a full-chip channelless routing system.

The research of this project focuses on the development of a performance-driven and routability-driven full-chip routing system in new advanced process. The routing system is mainly divided into two parts: performance-driven global routing and routability-driven full-chip detailed routing. In this project, a performance-driven global routing approach is prioposed in this year, We also hope that the research proposes an efficient routing integration for the design of SOC chips in new advanced process and gives a little valuable contribution for the development of VLSI design automation tools

**Keywords**: Advanced Process, SOC, Buffer Insertion, Wire Sizing

### 二、計劃緣由與目的

近年來,隨著對於高頻率晶片的需求,連線的延遲問題引起很大的注意與探討,一般而言,連線的延遲將由驅動邏輯

元件的電阻效應、線段的電容與電阻效應 計算而得。以往因為連線的電阻相較於驅 動邏輯元件的電阻效應為小,常常把線段 的電阻效應忽視不計。在新世代製程技術 中,隨著線段寬度的縮小,線段的電阻效 應反而比驅動邏輯元件的電阻效應更加顯 著,因此連線如何降低延遲反而成為維持 高效能設計的一個重要研究領域。

考慮連線延遲的降低,常常涉及延遲 模式的建立,現今之連線延遲模式常被視 為一個 RC 或 RCL 電路模式。在此電路延 遲模式中,包括降低驅動邏輯元件的電阻 效應、縮小電晶體的大小或憑藉著緩衝器 插入與線寬設定技巧來降低線段的電容與 電阻效應來達到減少連線延遲的目的,其 中以緩衝器插入(Buffer Insertion)與線寬設 定(Wire Sizing)技巧最常被用為降低連線 延遲的主要技巧。隨著高運算頻率晶片的 迫切需求,既然現今連線延遲所佔的重要 性又比元件延遲來得高,因此晶片中整體 連線延遲降低已成為高運算頻率晶片主要 解決的方向,對於高效能導向的總體繞線 的研究將是一個重要的領域。近年來已有 許多相關文獻討論在降低整體連線延遲之 整體繞線相關主題之上[1-5],但是這些文 獻大多著重在單一連線模式(Single-Net Model)的考量,並未考慮實際晶片實體佈 局上每條連線之繞線路徑形狀,如何利用 緩衝器插入與線寬設定技巧來降低連線的 延遲,因此在實體電路中的實用性仍有所 欠缺。另外在不考慮緩衝器插入情況下, 許多高效能導向的總體繞線方法[6-10]也 相繼被提出來降低繞線的最大延遲,但是 這些方法都沒有進一步考慮利用緩衝器插 入技巧來降低連線的延遲。

考量晶片實體佈局,每條連線之繞線 延遲雖可以靠緩衝器插入與線寬設定技巧 來減少,但也衍生緩衝器插入所產生的緩 衝器將如何安排在原來實體佈局上的問題,對於緩衝器區塊規劃的問題,在連線 導向的實體佈局上,已有探討緩衝器區塊 規劃方法[11-12]被提出以利緩衝器的插入 時有效地安排於緩衝器區塊中來減少整體 連線的延遲。有了固定緩衝器區塊的設定 之後,將可依緩衝器區塊的位置提出同步 繞線與緩衝器插入的方法[13]來完成繞線 樹形(Routing Tree),將可達到單一連線的 高效能導向總體繞線。但是這些方法都未 完整考量整個晶片實體佈局上的空間特 徵,無法充份利用晶片實體佈局的擺置特 性,來達到有效率的緩衝器區塊規劃與樹 形繞線的建構。在 SOC 晶片實體整合佈局 上,希望達到高效能需求,就得把連線上 的繞線樹形、線寬設定、緩衝器插入與緩 衝器區塊規劃並探討,才能滿足整體連線 延遲限制的要求。

## 三、結果與討論

本計畫不僅對於緩衝器規劃問題提出 新的以最佳線寬導向為基礎的緩衝器插入 解決模式,進一步對於繞線樹彈性度與總 體繞線方法的解法提出有效的可繞性解法, 希望如此之繞線方式能得到全晶片繞線成功,今年的計畫成果包含三個主要開發設 計部份:緩衝器規劃問題的設計、繞線樹 彈性度導向的開發與以全晶片總體繞線方 法設計,其成果如下所示:

#### (一) 緩衝器規劃問題的設計

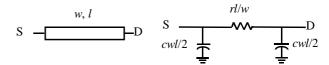

1. 最佳線寬與緩衝器數目的探討: 對於給 予線段之最佳線寬探討所得結果如 下: 倘若線段延遲模式如圖一所示,則

圖一 線段的 Elmore RC 延遲模式

$m{cru}$ 一: 給予長度為,l,之線段,為了降低此線段之延遲時間,則此線段之最佳線寬, $w_0^{op}$ ,為  $\sqrt{\frac{rC_{si}}{R_{so}c}}$  和最少延遲, $D_0^{opt}(l)$ ,

$$\frac{rc}{2} \left( \left( l + 2\sqrt{\frac{R_{so}C_{si}}{rc}} \right)^2 - \frac{2R_{so}C_{si}}{rc} \right)$$

**定理二**: 倘若一個緩衝器插入長度為, l, 之線段,則源頭至緩衝器之最佳線寬,  $w_i^{op}$ ,

為  $\frac{rC_b}{\sqrt{R_{so}c}}$ ,緩衝器至終端之最佳線寬, $w_2^{op}$ ,為  $\frac{rC_{si}}{\sqrt{R_{sc}}}$ ,緩 衝 器 最 佳 位 置 , $x_{op}$  ,為

$\frac{1}{2} + \frac{R_b w_2^{op} - R_{so} w_1^{op}}{2r} + \frac{\frac{C_{si}}{w_2^{op}} - \frac{C_b}{w_1^{op}}}{2c}$ ,與 最少延遲, $D_1^{op}(l)$ ,

$$\frac{rc}{4}l^{2} + \left(\frac{r}{2}\left(\frac{C_{si}}{w_{2}^{op}} + \frac{C_{b}}{w_{1}^{op}}\right) + \frac{c}{2}\left(w_{2}^{op}R_{b} + w_{1}^{op}R_{so}\right)\right)l$$

$$+\frac{\left(w_{2}^{op}R_{b}+w_{1}^{op}R_{ob}\left(\frac{C_{ol}}{w_{2}^{op}+\frac{C_{b}}{w_{1}^{op}}}\right)-\frac{r\left(\frac{C_{ol}}{w_{2}^{op}-w_{1}^{op}}\right)^{2}}{4c}-\frac{c\left(w_{2}^{op}R_{b}-w_{1}^{op}R_{ob}\right)^{2}}{4r}+T_{b}}{2}$$

定理三: 給予長度為, l, 之線段,連續緩 衝器間之最佳線長與線寬是相等的。

*定理四*: 給予具有最佳線寬, w;<sup>op</sup>, w<sup>op</sup>, 和 w<sup>op</sup>,長度為, l, 之線段, 為減少延遲時間, 插入此線段之最大緩衝器數, kmax,為

$$k_{\max} = \begin{vmatrix} -1 + \sqrt{1 + \frac{2rc(l + P_1 + P_3 - 2P_2)^2}{R_b C_b + T_b}} \\ 2 \end{vmatrix}$$

**定理五**: 給予長度為, l, 之線段,和所需 延遲時間,  $T_{req}$ , 當  $T_{req} \ge D^{op}(l)$  時, 滿足所 需延遲時間, $T_{rea}$ ,之最小緩衝器數, $k_{min}$ ,為

$$k_{\min} = \left[ \frac{-P_4 - \sqrt{P_4^2 - 4(R_bC_b + T_b)P_5}}{2(R_bC_b + T_b)} \right],$$

$$P_4 = rcP_5(l + P_1 + P_3 - 2P_2) - \frac{rc}{2}(P_1^2 + P_3^2 - 2P_2^2) + R_{in}C_b + R_bC_{ii} + T_b - T_{req},$$

\*\*In

$P_{5} = \frac{rc}{2} \left( l + P_{1} + P_{3} - 2P_{2} \right)^{2} + rcP_{2} \left( l + P_{1} + P_{3} - 2P_{2} \right) - \frac{rc}{2} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{si} - R_{b}C_{b} - T_{rec} \left( P_{1}^{2} + P_{3}^{2} - 2P_{2}^{2} \right) + R_{so}C_{b} + R_{b}C_{si} - R_{b}C_{si} -$

*定理六*:給予長度為, l, 之線段,和所需 延遲時間,  $T_{req}$   $(T_{req} \ge D^{op}(l))$ , 當個緩衝器 插入此線段,  $k_{\min} \leq k \leq k_{\max}$ , 則第一個緩衝 器的位置介於

$$\begin{split} \frac{-P_6 - \sqrt{P_6^2 - 4P_7}}{2} & \leq x \leq \frac{-P_6 + \sqrt{P_6^2 - 4P_7}}{2} \\ \text{,} \quad \not \sqsubseteq \dot P, \quad P_6 &= \frac{4k}{k+1} \sqrt{\frac{R_{so}C_b}{rc}} - \frac{2}{k+1} (l + P_1 + P_3 + (k-2)P_2), \quad \not \blacksquare \\ P_7 &= \frac{l^2}{k+1} + \frac{2l}{k+1} \Big( P_1 + P_3 + (k-2)P_2 \Big) + \frac{1}{k+1} \Big( P_1 + P_3 + (k-2)P_2 \Big)^2 \\ -\frac{k}{k+1} \Big[ P_1^2 + P_3^2 + (k-2)P_2^2 \Big] + \frac{2k}{k+1} \cdot \frac{R_{so}C_b + (k-1)R_bC_b + R_bC_{si} + kT_b - T_{req}}{rc} \end{split}$$

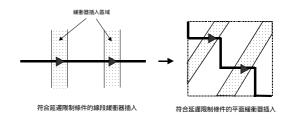

2. 緩衝器位置規劃:依據先前定理之結 果,緩衝器的位置的轉換如圖二表示與 圖三說明緩衝器之擺置結果。

二 線段與平面緩衝器插入的轉換

圖三 緩衝器插入後之擺置結果

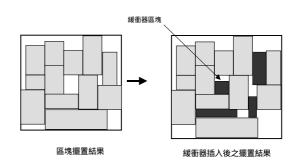

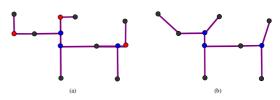

# (二) 繞線樹彈性度導向的開發

基本上繞線結果由繞線樹所構成.倘 若繞線樹的繞線彈性度能增加.則繞線結 果將增加全晶片可繞性。如圖四所示以繞 線相對面積定義繞線樹的繞線彈性度。藉 由史丹爾端點的移動,可達到具有如圖五 所示高彈性之繞線樹。

圖四 繞線樹的繞線彈性度

圖五 繞線樹的形成

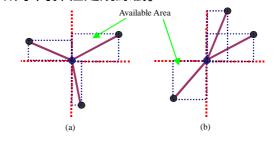

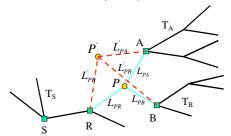

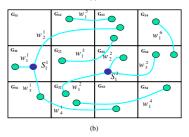

# (三). 全晶片總體繞線方法設計

對於全晶片總體繞線,以史丹爾端點 的移動為基礎,保障時序不被破壞的情況 下,達到減少擁擠現象,增加全晶片總體繞

# 線的可繞性。如圖六所示移動史丹爾端點 所產生之時序限制如下

$$\begin{split} & \left( \dot{L}_{PR} + \dot{L}_{PA} + \dot{L}_{PB} \right) (R_S + R_R) c - \left( L_{PR} + L_{PA} + L_{PB} \right) (R_S + R_R) c + \dot{L}_{PR} \left( \frac{\dot{L}_{PR}}{2} + \dot{L}_{PA} + \dot{L}_{PB} \right) c + C_A + C_B \right) r \\ & - L_{PR} \left( \frac{(\dot{L}_{PR}}{2} + L_{PA} + L_{PB}) c + C_A + C_B \right) r + \dot{L}_{PA} \left( \frac{\dot{L}_{PA}c}{2} + C_A \right) r - L_{PA} \left( \frac{\dot{L}_{PA}c}{2} + C_A \right) r \leq \underbrace{Minf}_{inf_A} \left\{ m_q(i) - t_A(i) \right\} \end{split}$$

圖六 史丹爾端點的移動

進一步依據史丹爾端點的移動,使得繞線 樹平衡的分佈在各個區域,減少擁擠程度 已達到如圖七所示全晶片整體繞線的結 果。

圖七 全晶片整體繞線

#### 四、記劃成果自評

在計畫執行期間依據本計劃之內容完成全晶片整體繞線的開發,主要完成的三個設計部份:緩衝器規劃問題的設計、繞線樹彈性度導向的開發與全晶片總體繞線方法設計,皆與原計畫內容完全相符、百分百達成預期目標。對於研究成果皆於近日整理陸續投稿於國外學術期刊,希望研究成果能提供在非分割型式擺置設計有效率之心得給有興趣之產學界參考。

# 五、參考文獻

- N. Menezes, S. Pullela, and L. T. Pileggi, "Simultaneous Gate and Interconnect Sizing for Circuit-Level Delay Optimization," *Proc. 32nd* ACM/IEEE Design Automation Conf., pp. 690–695, 1995.

- 2. T. Okamoto and J. Cong, "Buffered Steiner Tree Construction with Wire Sizing for Interconnect Layout Optimization," *Proc. Int'l Conf. on Computer-Aided Design*, 1996.

- 3. J. Oh, I. Pyo and M. Pedram, "Constructing Lower and Upper Bounded Delay Routing Trees Using Linear Programming," *Proc. 33rd Design Automation Conf.*, pp. 401–404, 1996.

- 4. S. S. Sapatnekar, "RC Interconnect Optimization Under the Elmore Delay Model," *Proc. ACM/IEEE Design Automation Conf.*, pp. 387-391, 1994.

- 5. L. P. P. van Ginneken, "Buffer Placement in Distributed RC-tree Networks for Minimal Elmore Delay," *Proc. Int'l Symp. on Circuits and Systems*, pp. 865-868, 1990.

- 6. J. Cong and C. K. Koh, "Interconnect Layout Optimization under High-order RLC model,", *Proc. Int'l Conf. on Computer-Aided Design*, pp.713-720, 1997.

- 7. J. Lillis, C. K. Cheng, T. T. Lin and C. Y. Ho, "New Performance-Driven Routing Techniques with Explicit Area/Delay Tradeoff and Simultaneous Wire Sizing," *Proc. 33rd Design Automation Conf.*, 1996, pp. 395–400.

- 8. J. Hu and S. S. Sapatnekar, "Performance Driven Global Routing Through Gradual Refinement", *Proc. Int'l Conf. on Computer-Aided Design*, pp.481-483, 2001.

- 9. H. Hou, J. Hu and S. S. Sapatnekar, "Non-Hanan Routing," *IEEE Trans. on Computer-Aided Design*, Vol.18, pp.436-444, 1999.

- Sapatnekar, 10. J. Hu S. "A and S. Timing-Constrained Simultaneous Global Algorithm", IEEETrans. onComputer-Aided Design, Vol.21, pp.1025-1036, 2002.

- 11. Jason Cong, T. Kong and D.Z. Pan "Buffer Block Planning for Interconnect-Driven Floorplanning", *Proc. ACM/IEEE International Conference on Computer Aided Design*, pp. 358-363, 1999.

- 12. P. Sarkar and C. K. Koh, "Routability-Driven Repeater Block Planning Interconnect-Centric Floorplanning," *IEEE Trans. on Computer-Aided Design*, Vol.20, pp.660-671, 2001.

- 13. Jason Cong and X. Yuan, "Routing Tree Construction Under Fixed Buffer Locations", Proc. *ACM/IEEE 37th Design Automation Conference*, pp. 379-384, 2000.