## 行政院國家科學委員會專題研究計畫 成果報告

## 行為層高效能處理器的容錯設計及快速驗證與容錯能力分 析(I) 研究成果報告(精簡版)

| 計 | 畫 | 類 | 別 | : | 個別型                    |

|---|---|---|---|---|------------------------|

| 計 | 畫 | 編 | 號 | : | NSC 95-2221-E-216-015- |

| 執 | 行 | 期 | 間 | : | 95年08月01日至96年07月31日    |

| 執 | 行 | 單 | 位 | : | 中華大學資訊工程學系             |

## 計畫主持人:陳永源

計畫參與人員:碩士班研究生-兼任助理:張坤鈞、石孟儒、吳耿偉

報告附件:出席國際會議研究心得報告及發表論文

處理方式:本計畫可公開查詢

## 中華民國 96年10月31日

The following report contains two parts: The first part is based on the fault injection approach to verify the capability of a fault-tolerant system. In this part, we propose a system-level simulation-based fault injection framework in SystemC design platform to assist the dependability assessment. The second part is going to discuss how to analyze the error coverage without using the fault injection and fault simulation mechanisms in order to save the development efforts and simulation time. Our idea is to devise a high-level abstract model to represent the fault-tolerant systems including the interconnection structure of the functional blocks, the propagation tables expressing the relationship between inputs and outputs for each functional block and the Petri Net to model the functional behavior of the fault-tolerant systems.

#### **Abstract** (first part)

This report describes the results achieved in the first year of three-year research proposal. As mentioned in the proposal, an important issue in the design of *SoC* with fault tolerance is how to verify the feasibility of the fault-robust design as early in the development phase to reduce the re-design cost. Therefore, a system-level fault-tolerant verification platform is required to assist the designers in assessing the dependability of a system with an efficient manner. The first part of this study is to propose a system-level simulation-based fault injection framework in SystemC design platform to assist the dependability assessment. The proposed fault injection framework is able to inject the faults into the systems modeled at the following levels of abstraction: register-transfer level (RTL)/bus-cycle accurate level, untimed functional transaction-level modeling with primitive channel sc\_fifo, and timed functional transaction-level modeling with hierarchical channel. We devise a distributed injection control approach instead of using one centralized control unit to control the injection technologies, is capable of injecting single or multiple faults with diverse fault types into different abstraction levels. We demonstrate the feasibility of the proposed fault injection framework with the modules modeled at different levels of abstraction.

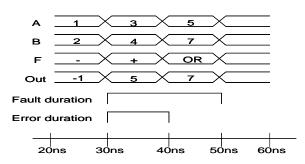

Another work of this study is to characterize the dependability of fault-tolerant systems modeled at different hardware design environments, SystemC and VHDL. For SystemC, we inject *errors* into the components' outputs, whereas *faults* into the inside of components for VHDL. The difference of the simulation results between SystemC and VHDL is discussed thoroughly through observing two parameters: one is the probability of a fault causing an effective error and another is the relationship between fault duration and error duration. The above two parameters dominate the discrepancy as seen between the two different design platforms. The experimental results show the effect of the fault attributes on the error coverage. This study can promote the fault-tolerant design and verification environment to a higher abstraction level. The preliminary results can be found in the appendix.

Keywords: fault-tolerant design, high-level abstraction modeling, high-level rapid verification, SystemC, system-level fault injection, system-on-chip (*SoC*), transient fault (soft error or SEU).

#### I. INTRODUCTION

As system-on-chip (SoC) becomes more and more complicated, and contains a large number of transistors, the SoC could encounter the reliability problem due to the increased likelihood of faults or radiation-induced soft errors especially when the chip fabrication enters the very deep submicron technology [1-3]. Thus, it is essential to employ the fault-tolerant techniques in the design of SoC to guarantee a high operational reliability in critical applications. However, due to the high complexity of the SoC, the incorporation of the fault-tolerant demand into the SoC will further raise the design complexity. Therefore, we need to adopt the behavioral level or higher level of abstraction to describe/model the SoC, such as using SystemC, to tackle the complexity of the SoC design and verification [4]. An important issue in the design of SoC with fault tolerance is how to validate the feasibility of the fault-robust design as early in the development phase to reduce the re-design cost. As a result, a system-level fault-tolerant verification platform is required to assist the designers in assessing the dependability of a system with an efficient manner. Normally, the fault injection approach is employed to verify the robustness of a fault-tolerant system.

SystemC [5], a system-level modeling language, provides a wide variety of modeling levels of abstraction and allows us to model a system utilizing one or a mixture of various abstraction levels. It is quite common that the

modules within a fault-tolerant *SoC* are modeled at different levels of abstraction using SystemC design language. Therefore, the fault injection framework for SystemC design platform must offer the methodologies to inject the faults into the different modeling levels.

Most of the previous fault injection studies focus on the VHDL design platform, whereas only a few works [6-9] address the fault injection issue in SystemC design platform. In our previous paper [9], we proposed a fault injection methodology for cycle-accurate register-transfer level (RTL) and compared the results of injection campaigns with the outcomes derived from the VHDL RTL. The comparisons show the accuracy and feasibility of our approach. However, the scheme presented in [9] can only apply to RTL, which limits the scope of application. In [6, 7], the authors proposed a fault injection framework that is applicable to functional level and transaction layer 1 in SystemC [10]. The mechanism presented in [6, 7] is based on the insertion of fault injection modules (FIMs) into the interconnections of the functional blocks, where a FIM is to control the fault injection activity for a selected fault target. The injection activity of a fault can be characterized by the following attributes: time instant, fault type/value, and fault duration. A centralized fault injection control unit is used to control the FIMs. So, the centralized control unit is responsible for the determination when to inject a fault into which target and for what fault value and duration. Once the centralized control unit decides to inject a fault, the related control signals are sent to the designated FIM. The

merit of [6, 7] scheme is no need to modify the SystemC source code for each fault injection campaign once the FIMs have been inserted into the simulation model. The only source to be prepared for each injection campaign is the fault injection controller that implements the injection script commands.

Several interesting issues deserved to be explored further are described as follows. One is the control complexity of the centralized injection control methodology and its effect on the simulation time. As system is getting more complex, the injection control complexity rises too. Consequently, the simulation performance could be degraded significantly. Another is how to inject the faults into the systems modeled using mixed levels of abstraction. Since it is rare that all modules within a system are modeled at the same level of abstraction, the injection approach developed should possess the ability to inject the faults into different levels of abstraction. Third is how to generate the fault injection script file at higher levels of abstraction in SystemC design platform, which represents the fault scenario for each injection campaign. The last issue is the feasibility of fault/error model employed at high level of abstraction. The precision of fault/error model will affect the accuracy of the results of injection campaign. Paper [9] presents a preliminary study of this fault/error modeling issue.

In this work, we propose an effective system-level simulation-based fault injection framework in SystemC design platform to assist the dependability assessment. The framework of fault injection proposed consists of the following modeling levels of abstraction: bus-cycle accurate (BCA) level, untimed functional transaction-level modeling (TLM) with primitive channel sc\_fifo, and timed functional transaction-level modeling with hierarchical channel. We devise a distributed injection control approach instead of using one centralized control unit to control the injection activity. The proposed distributed injection control approach is capable of injecting single or multiple faults with diverse fault types into different abstraction levels. Our scheme can inject the faults into a system modeled at mixed levels of abstraction in SystemC. As we see, the control of injection activity is distributed to the fault injection modules (FIMs), which may lower the control complexity of fault injection and the simulation time compared to the centralized control approach. However, our approach needs to construct the source code of SystemC simulation model for each fault injection campaign because the fault injection script commands are distributively implemented in each FIM. The comparison of our distributed approach with the centralized control method in terms of experiment setup, compiling time, fault injection efficiency and simulation time will be discussed in the future.

The remaining report is organized as follows. In Section 2, the fault injection framework is presented. We demonstrate the feasibility of our fault injection approach in Section 3. The conclusions and future work appear in Section 4.

#### **II. FAULT INJECTION FRAMEWORK IN SYSTEMC**

In this section, we consider the fault injection into the communication channels at the following abstraction levels.

The first one is sc\_signal at BCA level; the second one is the primitive channel sc\_fifo at untimed functional transaction level and the last on is the hierarchical channel [5, 10] at timed functional transaction level. The principal idea of our approach is based on the insertion of FIMs into the interconnections of the functional blocks, where a FIM is to control the fault injection activity for the selected fault target. Since we distribute the injection control to each FIM, the FIMs are responsible for the determination of the fault injection activity including when to inject a fault, what the fault value and its duration. The core of the FIM design is how to decide when to activate a fault injection.

#### A. Fault injection at BCA level

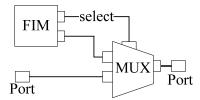

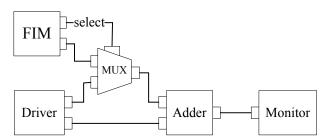

Fig. 1 shows the fault injection structure for BCA level that includes a FIM used for the control of fault injection. The FIM contains an injection list of the faults, which depicts the injection activity for each fault collected in the injection list. Since the BCA level is clock-cycle accurate, the FIM can use the sc\_simulation\_time () to get the time instant of the beginning of each clock cycle. Then, the FIM checks the current time instant obtained with the injection time list of the faults pre-specified in the FIM. If the time instant is equal to the injection time of a fault, FIM will activate the fault injection by generating the desired fault type/value to the 'MUX' input port and keep the fault stayed active for a pre-defined length of time; otherwise, the original signal is delivered.

Fig. 1. Fault injection structure for BCA level.

#### B. Fault injection at untimed functional transaction level

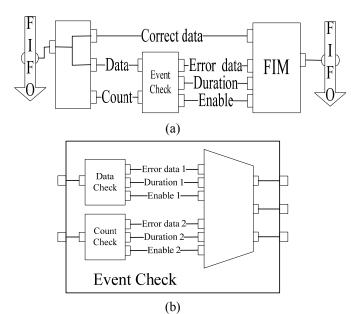

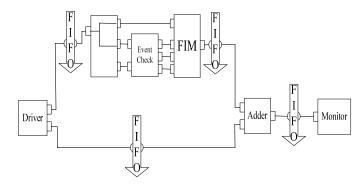

As no clock exists in this level of abstraction, the event-driven method is utilized to trigger the FIM as illustrated in Fig. 2. An event is used to represent a condition that may occur during the course of simulation and to control the triggering of fault injection. We create the 'Event Check' module to monitor the occurrence of a specific event to control the FIM when to trigger the fault injection. The event could be, for example, a particular instruction address or a counter whose value reaches to a specific count. When the declared event occurs, the 'Event Check' module will send a trigger signal 'Enable' to FIM to activate the fault injection.

Fig. 2(b) exhibits the circuit diagram of 'Event Check' block. The 'Data Check' module can check the data-related events, such as a particular address and data. The 'Count Check' can check, for example, whether the number of data read out from the FIFO channel has reached to a specific count. Table I presents the operation of 'Event Check'. 'Event Check' is expandable if more types of events need to check.

Fig. 2. (a) Fault injection structure for channel sc\_fifo. (b) The circuit diagram of 'Event Check'

| TABLE I THE | OPERATION OF | 'Event | Check'. |

|-------------|--------------|--------|---------|

|-------------|--------------|--------|---------|

| Data    | Count    |             |           |         |

|---------|----------|-------------|-----------|---------|

| Enable1 | Enable 2 | Data        | Duration  | Enable  |

| 0       | 0        | 0           | 0         | 0       |

| 0       | 1        | Error data2 | Duration2 | Enable2 |

| 1       | 0        | Error data1 | Duration1 | Enable1 |

| 1       | 1        | Error data1 | Duration1 | Enable1 |

#### C. Fault injection at timed functional transaction level

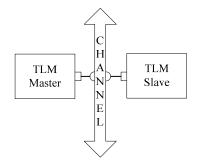

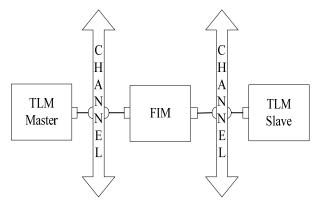

Fig. 3 shows the transaction-level channel structure. Fault injection structure for transaction-level hierarchical channel is illustrated in Fig. 4. We note that a redundant channel is inserted between FIM and Slave modules. It is because the port of Slave module is the connection type for channel. To keep the original source code unchanged, we add one more channel to connect the FIM and Slave modules. This redundant channel is injection-induced component. Apparently, the input port and output port of FIM are slave port and master port for channel connection. Here, the concept of FIM is similar to that of sc\_fifo.

In next section, we will exploit a popular hierarchical channel: AMBA bus to demonstrate the fault injection platform displayed in Fig. 4. We use the AMBA bus library [12] and AMBA bus API (Application Programming Interface) [13] provided by CoWare Platform Architect to implement the FIM as shown in Fig. 4.

Fig. 3. Transaction-level channel structure.

Fig. 4. Fault injection structure for transaction-level hierarchical channel.

#### **III. FAULT INJECTION DEMONSTRATION**

The following experimental studies were performed to validate the feasibility of our fault injection framework proposed in Section II. Fig. 5 shows a common circuit structure used in fault injection experiments. In Fig. 5, 'Driver' module is responsible for generating the augend and addend to the adder; 'Monitor' module is for printing out the results of adder. We employ the CoWare Platform Architect v2005.1.1 to build up the experimental environment.

#### A. Experiment at BCA level

Fig. 6 illustrates the fault injection structure of Fig. 5 circuit, where the modeling level of this experiment is BCA style. The clock cycle is 5 ns in this fault injection experiment. 'Driver' module sends out the augend and addend to the adder every 5 ns, where we assign zero to augend all the time and one to eight in sequence to addend. Two faults are injected into the augend through FIM at different simulation time. The first fault is injected at 15 ns. At that time, FIM delivers the fault value twelve to 'MUX' input port and sets 'select' signal to pass the fault value to the input port of 'Adder'. The duration of this fault is two clock cycles. The second fault is injected at 30 ns with fault value twenty and lasts one clock cycle. Fig. 7 presents the simulation results of fault-free and fault injection experiments. As can be seen from Fig. 7, it is evident that the first fault appears at time 15 ns and sustains two clock cycles. Another fault happens at time 30 ns and lasts one cycle. The injection capability of our approach at BCA level is justified from the results of fault injection campaign as shown in Fig. 7.

#### B. Experiment at untimed functional transaction level

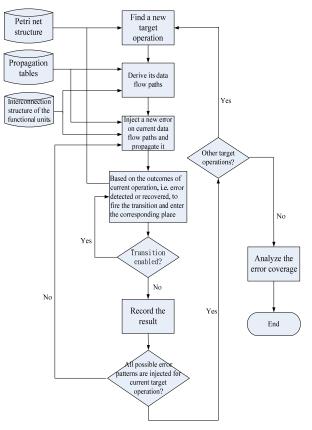

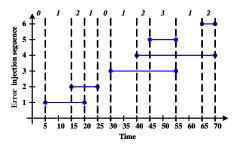

Fig. 8 illustrates the fault injection structure at untimed functional transaction level. Table II lists a fault scenario for the injection campaign. From Table II, we see that the 'Count Check' will activate the fault injection while the 'Count' event , i.e. the number of augend data read out from the FIFO channel, has reached to a particular count, 1, 4 and 7, respectively. In this experiment, the augend values are (0, 2, 0, 4, 0, 6, 0, 8, 0, 10, 0, 12, 0, 14, 0, 16) and the addend values are (1, 0, 3, 0, 5, 0, 7, 0, 9, 0, 11, 0, 13, 0, 15, 0). Fig. 9 shows the results of the fault-free and fault injection experiments. From Fig. 9, it is easy to see that the

first three faults are count-triggered faults and sustain one, two and three transactions, respectively. The last fault is data-triggered fault and maintains two transactions long. The simulation outcomes of Fig. 9 confirm the feasibility of event-triggered injection approach for untimed functional transaction level.

#### C. Experiment at timed functional transaction level

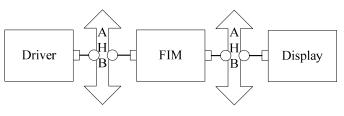

In this experiment, we employ the AMBA bus to demonstrate the injection of faults into the hierarchical channels modeled at timed functional transaction level. Since hierarchical channel plays an important role in SoC, offering the injection capability of faults into the hierarchical channels is imperative in SystemC design platform. We utilize the AMBA bus library [12] and AMBA bus API [13] furnished by CoWare Platform Architect to implement the circuit diagram shown in Fig. 10. The 'Driver (master)' and 'Display (slave)' modules in Fig. 10 are responsible for sending data to AHB and receiving plus printing data from AHB respectively. The concept of FIM module is like 'AHB to AHB Bridge' except FIM is able to pollute the bus data during the fault injection campaign. The count of data transaction in AHB is used in FIM to decide the injection time of faults. In this demonstration, two faults are injected into the AHB channel. The first fault occurs at the second data transaction and lasts the length of two data transactions. The second fault happens at the tenth data transaction and sustains one data transaction. The simulation results of fault-free and fault injection experiments are exhibited in Fig. 11.

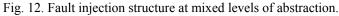

#### D. Experiment at mixed levels of abstraction

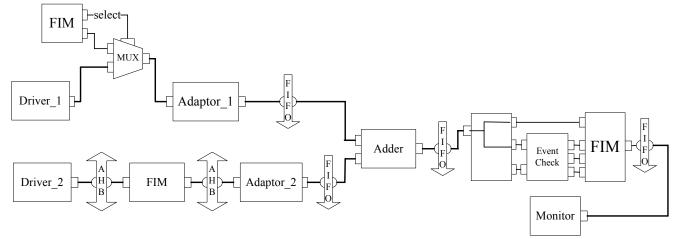

SystemC, as a system-level design platform, employs the concepts of intellectual property (IP) reuse and hierarchical channel to reduce the *SoC* design complexity, effort and time. However, the provided IP modules may be modeled at various levels of abstraction such that a system is often modeled at mixed abstraction levels. Therefore, the inclusion of fault injection at mixed levels of abstraction is important in the development of system-level fault injection framework. The goal of this experiment is to show the feasibility of our fault injection framework, which is capable of injecting the faults into a system modeled at mixed levels of abstraction.

Fig. 12 demonstrates a fault injection structure at mixed levels of abstraction. In Fig. 12, 'Driver 1' module modeled at RTL provides the augend data for 'Adder'; 'Driver 2' module modeled at timed functional transaction level offers the addend data through the AHB channel to 'Adder', and right part of Fig. 12 including 'Adder' and 'Monitor' modules is modeled at untimed functional transaction level with primitive channel sc fifo. 'Driver 1' sends out an augend every 5 ns following the data sequence  $0 \sim 14$ . 'Driver 2' sends out an addend every 10 ns following the data sequence  $0 \sim 14$ . The 'Adder' module synchronizes the input sequences of augend and addend, and therefore, the results of 'Adder' are  $2 \times i$ , i = 0 to 14. The fault scenario for this experiment is as follows: 'FIM' in 'Driver 1' part injects faults into augend at time 15ns and 25 ns; 'FIM' in 'Driver 2' part injects faults into addend at transaction count 6 and 9; 'FIM' in 'Monitor' part injects faults into 'Monitor' input at transaction count 11 and 12, and at 'Adder' output data equal to 28. Fig. 13 illustrates the simulation results of fault-free and fault injection experiments. As can be seen from Fig. 13(a), a situation of multiple faults occurs when augend is 55 and addend is 200. This confirms the multiple fault injection ability of our mechanism.

Fig. 5. A common circuit structure for injection experiments.

Fig. 6. Fault injection structure of Fig. 5 circuit modeled at BCA level.

| ▼ Term                                                                             | Terminal                                                                           |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>T</u> erminal Ta <u>b</u> s <u>H</u> elp | <u>Fi</u> le <u>E</u> dit <u>V</u> iew <u>T</u> erminal Ta <u>b</u> s <u>H</u> elp |

| SystemC 2.1.v1 Jul 6 2                                                             |                                                                                    |

| Copyright (c) 1996-2005 by all C<br>ALL RIGHTS RESERVED                            | Copyright (c) 1996-2005 by all Contributors<br>ALL RIGHTS RESERVED                 |

| at time : O s::                                                                    | at time : 0 s::                                                                    |

| The result of the error free is = 0                                                | The result of the error injection is = 0                                           |

| at time : O s::                                                                    | at time : 0 s::                                                                    |

| The result of the error free is = $1$                                              | The result of the error injection is = 1                                           |

| at time : 5 ns::                                                                   | at time : 5 ns::                                                                   |

| The result of the error free is = 2                                                | The result of the error injection is = 2                                           |

| at time : 10 ns::                                                                  | at time : 10 ns::                                                                  |

| The result of the error free is = 3                                                | The result of the error injection is = 3                                           |

| at time : 15 ns::                                                                  | at time : 15 ns::                                                                  |

| The result of the error free is = 4                                                | The result of the error injection is = 16                                          |

| at time : 20 ns::                                                                  | at time : 20 ns::                                                                  |

| The result of the error free is = 5                                                | The result of the error injection is = 17                                          |

| at time : 25 ns::                                                                  | at time : 25 ns::                                                                  |

| The result of the error free is = 6                                                | The result of the error injection is = 6<br>at time : 30 ns::                      |

| at time : 30 ns::                                                                  |                                                                                    |

| The result of the error free is = 7<br>at time : 35 ns::                           | The result of the error injection is = 27<br>at time : 35 ns::                     |

| at time : 35 ns::<br>The result of the error free is = 8                           | The result of the error injection is = 8                                           |

|                                                                                    | SystemC: simulation stopped by user.                                               |

| SystemC: simulation stopped by user.                                               | [Thread debugging using libthread_db enabled]                                      |

| [New Thread -1208059584 (LWP 9466)]                                                | [New Thread -1208059584 (LWP 9355)]                                                |

| [Mem III.ean -1700033204 (TML 3400)]                                               | [[uem THTEar -TTOPO12101 (TML 2000)]                                               |

Fig. 7. Simulation results of fault-free (left side) and fault injection (right side) experiments at BCA level.

Fig. 8. Fault injection structure at untimed functional transaction level.

#### TABLE II FAULT EVENTS, VALUES AND DURATION

| Count check | Fault value | Fault duration |

|-------------|-------------|----------------|

| 1           | 11          | 1              |

| 4           | 44          | 2              |

| 7           | 77          | 3              |

| Data check | Fault value | Fault duration |

|------------|-------------|----------------|

| 12         | 222         | 2              |

| Y Te                                                               | Terminal                                         |

|--------------------------------------------------------------------|--------------------------------------------------|

| <u>File Edit V</u> iew <u>T</u> erminal Ta <u>b</u> s <u>H</u> elp | <u>File Edit View Terminal Tabs H</u> elp        |

| Copyright (c) 2004 Cade                                            | c Copyright (c) 2004 Cadence, Inc.               |

| 2655 Seely Avenue, San Jose, C                                     |                                                  |

|                                                                    |                                                  |

| SystemC 2.1.v1 Jul                                                 | SystemC 2.1.v1 Jul 6 2006 18                     |

| Copyright (c) 1996-2005 by al                                      |                                                  |

| ALL RIGHTS RESERV                                                  |                                                  |

| The result of the error free is = 1                                | The result of the error injection is = 12        |

| The result of the error free is = 2                                | The result of the error injection is = 2         |

| The result of the error free is = 3                                | The result of the error injection is = 3         |

| The result of the error free is = 4                                | The result of the error injection is = 44        |

| The result of the error free is = $5$                              | The result of the error injection is = 49        |

| The result of the error free is = 6                                | The result of the error injection is = 6         |

| The result of the error free is = 7                                | The result of the error injection is = 84        |

| The result of the error free is = 8                                | The result of the error injection is = 77        |

| The result of the error free is - 9                                | The result of the error injection is = 86        |

| The result of the error free is = 10                               | The result of the error injection is = 10        |

| The result of the error free is = 11                               | The result of the error injection is = 11        |

| The result of the error free is = 12                               | The result of the error injection is = 222       |

| The result of the error free is = 13                               | The result of the error injection is = 235       |

| The result of the error free is = 14                               | The result of the error injection is = 14        |

| The result of the error free is = 15                               | The result of the error injection is = 15        |

| The result of the error free is = 16                               | The result of the error injection is = 16        |

| SystemC: simulation stopped by user.                               | SystemC: simulation stopped by user.             |

| [Thread debugging using libthread_db                               | en [Thread debugging using libthread_db enabled] |

Fig. 9. Simulation results of the fault-free and fault injection experiments at untimed functional transaction level.

Fig. 10. Fault injection structure at timed functional transaction level.

| Y                                                                          | 🕑 Terminal                                                                            |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <u>File E</u> dit <u>V</u> iew <u>T</u> erminal Ta <u>b</u> s <u>H</u> elp | <u>File E</u> dit <u>V</u> iew <u>T</u> erminal Ta <u>b</u> s <u>H</u> elp            |

| SystemC 2.1.v1 Jul<br>Copyright (c) 1996-2005 by a<br>ALL RIGHTS RESER     |                                                                                       |

| Speed optimizations of HARDWARE.i_AH<br>ddr.                               | Speed optimizations of HARDWARE.i_AHB.i_AHB d                                         |

| The Data of the error free = 0                                             | The Data of the error injection = 0                                                   |

| The Data of the error free = 1<br>The Data of the error free = 2           | The Data of the error injection = 200<br>The Data of the error injection = 200        |

| The Data of the error free = 3                                             | The Data of the error injection = 3                                                   |

| The Data of the error free = 4<br>The Data of the error free = 5           | The Data of the error injection = 4<br>The Data of the error injection = 5            |

| The Data of the error free = 6                                             | The Data of the error injection = 6                                                   |

| The Data of the error free = 7<br>The Data of the error free = 8           | The Data of the error injection = 7<br>The Data of the error injection = 8            |

| The Data of the error free = 9<br>The Data of the error free = 10          | The Data of the error injection = 100<br>The Data of the error injection = 10         |

| The Data of the error free = 11                                            | The Data of the error injection = 11                                                  |

| The Data of the error free = 12<br>The Data of the error free = 13         | The Data of the error injection = 12<br>The Data of the error injection = 13          |

| The Data of the error free = 14                                            | The Data of the error injection = 14                                                  |

|                                                                            | [Thread debugging using libthread_db enabled]<br>[New Thread -1208059584 (LWP 10305)] |

|                                                                            | [New SystemC Thread "main" 169690880]<br>[New Thread -1208730720 (LWP 10308)]         |

Fig. 11. Simulation results of the fault-free and fault injection experiments at timed functional transaction level.

| ſ     | <b>v</b>     |              |              |       |        |               | T                  |              |              |              |                  |               | ///////      | Terminal   |

|-------|--------------|--------------|--------------|-------|--------|---------------|--------------------|--------------|--------------|--------------|------------------|---------------|--------------|------------|

|       | <u>F</u> ile | <u>E</u> dit | <u>V</u> iew | Ter   | minal  | Ta <u>b</u> s | <u>H</u> elp       | <u>F</u> ile | <u>E</u> dit | <u>V</u> iew | <u>T</u> erminal | Ta <u>b</u> s | <u>H</u> elp |            |

| ÷     |              |              |              |       |        |               |                    |              |              |              |                  |               |              |            |

|       |              |              | S            | ystem | nC 2.1 | .v1 -         | Jul                |              |              | Sy           | stemC 2.         | 1.v1 -        | Ju]          | 6 2006 1   |

|       |              | Co           | pyri         | ght ( | (c) 19 | 96-20         | 05 by al           |              | Co           | pyrig        | ht (c) 1         | 996-20        | 05 by        | all Contri |

| Т     |              |              |              |       |        |               | 'S RESERV          |              |              |              |                  | RIGHT         |              |            |

|       |              | d opti       | miza         | tions | s of H | IARDWA        | RE.i_AHB           | Spee         | ed opti      | imizat       | ions of          | HARDWA        | RE.i_A       | HB.i_AHB d |

| - IE  | ddr.         |              |              |       |        |               |                    | ddr.         |              |              |                  |               |              |            |

| - H.  |              |              |              |       |        |               | is = 0             |              |              |              | he error         |               |              |            |

| - H L |              |              |              |       |        |               | is = 2             |              |              |              | he error         |               |              |            |

|       |              |              |              |       |        |               | is = 4             | _            |              |              | he error         |               |              |            |

|       |              |              |              |       |        |               | is = 6             |              |              |              | he error         |               |              |            |

|       |              |              |              |       |        |               | is = 8             |              |              |              | he error         |               |              |            |

| _     |              |              |              |       |        |               | is = 10            |              |              |              | he error         |               |              |            |

| - IL  |              |              |              |       |        |               | is = 12            |              |              |              | he error         |               |              |            |

|       |              |              |              |       |        |               | is = 14<br>is = 16 |              |              |              | he error         | -             |              |            |

|       |              |              |              |       |        |               | 1s = 16<br>is = 18 |              |              |              | he error         |               |              |            |

| -     |              |              |              |       |        |               | is = 20            |              |              |              | he error         | 0             |              |            |

|       |              |              |              |       |        |               | is = 20<br>is = 22 |              |              |              | he error         |               |              |            |

|       |              |              |              |       |        |               |                    |              |              |              | he error         | -             |              |            |

|       |              |              |              |       |        |               | is = 26            |              |              |              | he error         |               |              |            |

|       |              |              |              |       |        |               | is = 28            |              |              |              |                  |               |              | s = 2828   |

|       |              |              |              |       |        |               | read_db            |              |              |              |                  |               |              | b enabled] |

|       |              |              | 00           |       |        |               | 10839)]            |              |              |              | 08059584         |               |              |            |

|       | [New         | Syste        | mC T         | hread | d "mai | n" 16         | 69711456]          |              |              |              | read "ma         |               |              |            |

| 1     |              |              |              |       |        |               | -                  | <u> </u>     |              |              |                  |               |              | -          |

(b)

Fig. 13. (a) Fault injection scenario. (b) Simulation results of fault-free and fault injection experiments.

#### IV. CONCLUSIONS AND FUTURE WORK

In this report, a system-level fault injection framework in SystemC design platform is presented. The proposed fault injection framework provides the methodologies for injecting the faults into various levels of abstraction. Three modeling levels considered in the framework are BCA level, untimed functional transaction level, and timed functional transaction level. The experiments based on CoWare Architect Platform were conducted to validate the feasibility of our fault injection approach. Contributions of this work are first to present the idea of distributed fault injection control to lower the control complexity of the fault injection compared to the centralized fault injection control; to develop the methodologies, including the time-triggered and event-triggered concepts, to inject the faults into different abstraction levels, and importantly to provide a solution for injection of faults into a system modeled at various levels of abstraction.

In the future, we will further explore the approach of distributed control of fault injection and compared to the method of centralized control of fault injection in terms of the complexity of experiment setup, compiling time, fault injection efficiency and simulation time. In addition, we will implement the proposed fault injection framework in the EDA tool of CoWare Architect Platform.

### REFERENCES

- C. Constantinescu, "Impact of Deep Submicron Technology on Dependability of VLSI Circuits," *IEEE Intl. Conf. On Dependable Systems and Networks* (DSN), pp. 205-209, 2002.

- [2] P. Shivakumar et al., "Modeling the Effect of Technology Trends on the Soft Error Rate of Combinational Logic," DSN, pp. 389-398, 2002.

- [3] T. Karnik, P. Hazucha, and J. Patel, "Characterization of Soft Errors Caused by Single Event Upsets in CMOS Processes," *IEEE Trans. on Dependable and*

Secure Computing, Vol. 1, No. 2, pp. 128-143, April-June 2004.

- [4] A. Fin, F. Fummi and G. Pravadelli, "AMLETO: a Multilanguage environment for functional test generation", 2001 International Test Conference, pp. 821-829, Nov. 2001.

- [5] Grotker Thorsten et al., "System Design with SystemC," Kluwer Academic Publishers, 2002.

- [6] K. Rothbart et al., "High Level Fault Injection for Attack Simulation in Smart Cards," 13th Asian Test Symposium, pp. 118-121, Nov. 2004.

- [7] K. Rothbart et al., "A Smart Card Test Environment Using Multi-Level Fault Injection in SystemC", 6th IEEE Latin-American Test Workshop, pp. 103-108, March-April 2005.

- [8] K. Rothbart et al., "Power Consumption Profile Analysis for Security Attack Simulation in Smart Cards at High Abstraction Level," *EMSOFT*, pp. 214-217, Sept. 2005.

- [9] Kuen-Long Leu, Yung-Yuan Chen, and Jwu-E Chen, "A Comparison of Fault Injection Experiments under Different Verification Environments", *IEEE Fourth International Conference on Information Technology and Applications*, pp. 582-587, Jan. 2007.

- [10] Open SystemC Initiative (OSCI), "SystemC 2.0 Language Reference Manual," Revision 1.0, <u>www.systemc.org</u>, 2003.

- [11] Bhasker Jayaram and J. Bhasker, "A SystemC Primer," Star Galaxy Publisher, 2004.

- [12] CoWare Model Library, "AMBA Bus Library," Product Version V2005.2.2.

- [13] CoWare Model Library, "TLM API Manual," Product Version V2005.

## **Abstract (second part)**

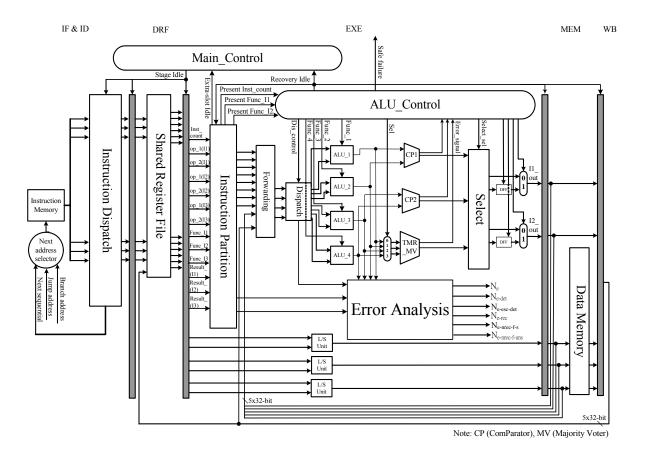

This report describes the results achieved in the first year of three-year research proposal. As mentioned in the proposal, an important issue in the design of *SoC* with fault tolerance is how to verify the feasibility of the fault-robust design as early in the development phase to reduce the re-design cost. Therefore, a system-level fault-tolerant verification platform is required to assist the designers in assessing the dependability of a system with an efficient manner. The second part is going to discuss how to analyze the error coverage without using the fault injection and fault simulation mechanisms in order to save the development efforts and simulation time. Our idea is to devise a high-level abstract model to represent the fault-tolerant systems including the interconnection structure of the functional blocks, the propagation tables expressing the relationship between inputs and outputs for each functional block and the Petri Net to model the functional behavior of the fault-tolerant system. The fault-tolerant verification platform proposed here can save the time of detailed hardware implementation, benchmark program development, and fault injection campaigns. As a result, it is efficient to reduce the implementation and validation efforts. However, since our approach employs a high level of abstraction to model the fault-robust systems, the accuracy of the simulation results will decrease. A fault-tolerant VLIW core developed by our team is used to demonstrate the feasibility of our approach by comparing the results obtained from this approach with the results derived from the simulation-based fault injection technique by VHDL.

**Keywords:** error propagation path, high-level abstraction modeling, high-level rapid verification, Petri Net, system-on-chip (*SoC*), transient fault (soft error or SEU).

### **INTRODUCTION**

Due to the high complexity of the system-on-chip (SoC), the behavioral level or higher abstraction level are used to model the SoC so as to tackle the complexity of the SoC design. It is well known that the rate of radiation-induced soft errors increases rapidly especially in combinational logic while the chip fabrication enters the deep submicron technology [1-3]. Such influences raise the urgent need to incorporate the fault tolerance into the high-performance systems [4-7]. However, the incorporation of the fault-tolerant demand into the SoC will further complicate the design problem. Importantly, we need to verify the feasibility of the fault-robust design as early in the development phase to reduce the re-design cost. Therefore, a system-level fault-tolerant verification platform is required to assist the designers in assessing the dependability of a system with an efficient manner.

We can validate the dependability of fault-tolerant systems by fault injection campaigns [8-10]. In general, the verification process of system robustness is performed by injecting the faults into the system and monitoring whether the faults are detected/recovered or cause the system failure, etc. The fault injection techniques presented in the previous literature can be classified as physical [11]. software-implemented [12] and simulation-based [13, 14] fault injection approaches. The different classes of fault injection approaches provide a compromise between implementation efforts, simulation time and the accuracy of the experimental results. A major of physical limitation and software-implemented approaches is that dependability evaluation is performed physical systems have been built. after While dependability evaluation is necessary after systems have been built, the costs of re-designing systems due to inadequate dependability can be prohibitively expensive. The simulation-based fault injection uses the simulation to inject faults in simulation models of systems. The simulation model of systems can be described in hardware description language like VHDL. The advantage of simulation-based mechanism is that the system dependability can be assessed as early in the design phase, and if necessary to re-design the system, the cost of re-design is reduced significantly. Although the

simulation-based approach shows a valuable means to support the validation of the fault-tolerant systems, it still requires considerable efforts to model the system implementation at different abstraction levels, to develop the benchmark programs as well as the fault injection tools, and to perform the fault injection campaigns. The goal of this study is to propose a new fault-tolerant verification approach that can significantly reduce the validation efforts compared to the simulation-based approach.

As discussed before, several issues should be addressed in the fault-tolerant verification process: First is the way of faults/errors injected; second is the paths of faults/errors propagated and third is the outcomes of faults/errors processed and analyzed. It is clear that the verification efficiency can be enhanced if we can more effectively cope with the above issues. For this purpose, we devise a high-level abstract modeling methodology to modeling the fault-tolerant systems where the emphasis of system modeling is more on the error propagation and error handling, and less on the details of the implementation of the functional units. Since the proposed modeling methodology focuses on the function of fault-robust validation only, the complexity of system models will decrease. Therefore, it reduces the efforts to modeling the systems and the time to performing the fault injection campaigns and error coverage analysis. However, since our fault-tolerant verification approach employs a high level of abstraction to modeling the systems, the accuracy of the simulation results could be hurt.

The rest of the report is organized as follows: In Section 2, the methodology to modeling the fault-robust systems is proposed. Section 3 uses a fault-tolerant VLIW core to demonstrate the proposed fault-tolerant verification approach. In Section 4, the simulation results are provided and compared with the results derived from the simulation-based fault injection approach by VHDL. The conclusions appear in Section 5.

## FAULT-ROBUST SYSTEM MODELING METHODOLOGY

The goal of the modeling methodology is to lower the complexity of the modeling, simulation and analysis of the fault-tolerant systems. The basic idea is to find out the data flow paths of each system operation. Then, locate all possible errors which could occur in the data flow paths for a particular operation under a specific error model. For each operation, we can inject the desired errors from the error model into the corresponding data flow paths and check whether the detection and recovery schemes embedded in the system can tolerate the errors or not. To support the validation of system robustness, the proposed system model must have the capability to propagate the errors while the system is executed.

Based on the above discussion, we develop a high-level abstract model to modeling the fault-robust systems. The simulation model of systems comprises the following three parts:

- 1. the interconnection structure of the functional units;

- 2. the propagation tables expressing the relationship between inputs and outputs for each functional unit;

- 3. the Petri net structure [15] to model the functional behavior of the fault-tolerant systems.

More specifically, the propagation tables can be utilized to propagate the errors from the inputs to the outputs of each functional unit. And through the interconnections of the functional units, the effect of errors will be propagated. An abstract error model is exploited to generate the desired error patterns for the system under validation. The function of Petri net model is to control the operations of the system. For each operation represented by a place in the Petri net graph, we also need to store its control signals for the corresponding functional units which are responsible for the execution of the operation. We can count on the Petri net model and the control signals for each operation to derive the corresponding data flow paths for a particular operation. Then, all possible errors which could happen in those data flow paths for a specific operation can be located. In that way, we can generate the error list for each operation. In other words, our verification approach can produce the propagation paths for each error to see whether the paths of error propagation have the detection and recovery protection or not. Therefore, we can examine the error patterns one by one for a particular operation to acquire the dependability data for robustness validation. Finally, the error coverage of a system can be derived from the detailed analysis of the error coverage related to each operation. In addition to the error coverage evaluation, the analysis can also discover the single failure points or weak points of the systems that can be utilized to improve the system dependability further.

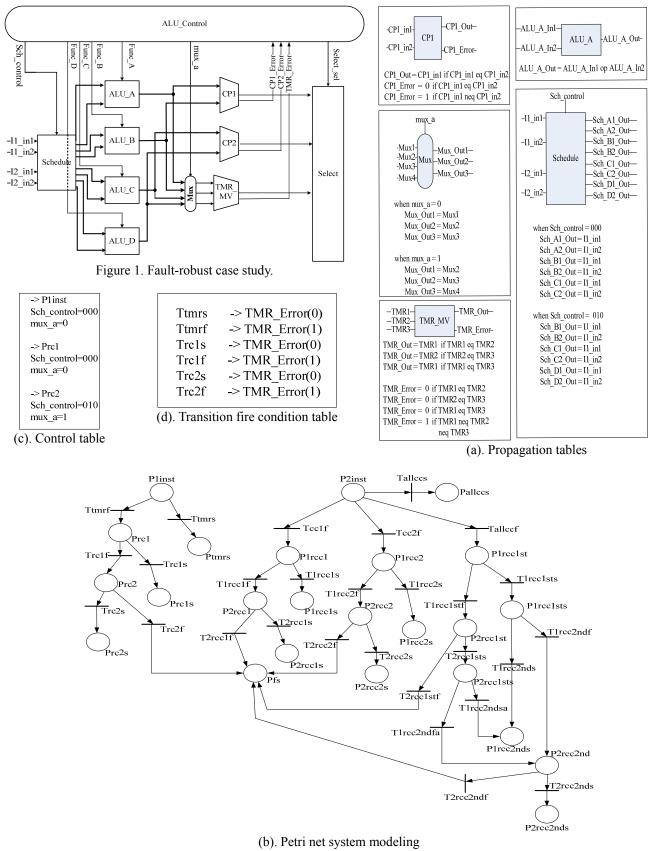

#### CASE STUDY

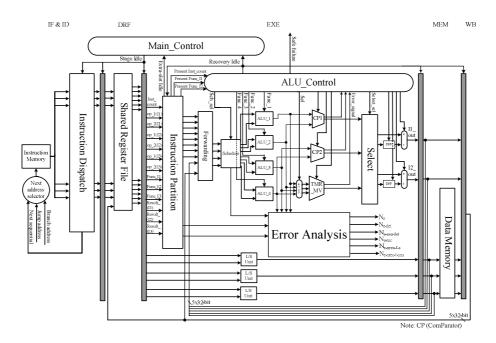

A fault-tolerant VLIW core [16] is used to demonstrate the concept of our approach. For simplicity of demonstration, we adopt the portion of the execution stage of VLIW core as shown in Figure 1 to illustrate the modeling methodology and the fault-robust verification process. In Figure 1, 'CP' and 'TMR\_MV' denote the 'comparator' and 'triple modular redundancy majority voter', respectively. The fault-tolerant scheme employed in [16] is briefly described as follows:

while (not end of program)

- {switch (Number of instructions in an execution packet for ALU.)

- {case '1': TMR\_MV(ALU\_1, ALU\_2, ALU\_3); if

(TMR\_MV detects more than one ALU failure) then the "Error-recovery process" is activated to recover the failed instruction.

case '2': the execution packet contains two instructions:  $I_1$  and  $I_2$ .

I<sub>1</sub>: CP1(ALU\_1, ALU\_2);

I<sub>2</sub>: CP2(ALU\_3, ALU\_4);

if  $(I_1 \text{ fails})$  then the "Error-recovery process" is activated to recover  $I_1$ .

if  $(I_2 \text{ fails})$  then the "Error-recovery process" is activated to recover  $I_2$ .

case '3':the packet is divided to two packets and executed sequentially.

#### **Error-recovery process:**

$i \leftarrow 1;$

While (number of retries  $r_{no} > 0$ )

$\{\text{TMR}_{\text{MV}}(\text{ALU}_{i}, \text{ALU}_{i}+1, \text{ALU}_{i}+2);$

if (TMR\_MV succeeds) then the error recovery succeeds  $\rightarrow$  exit;

else {

$$r\_no \leftarrow r\_no-1$$

;  $i \leftarrow i+1$  ; if  $(i \ge 3)$  then  $i \leftarrow 1$ ;}}

recovery failure and the system enters the fail-safe state.

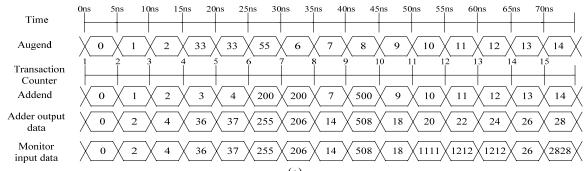

Figure 2 exhibits the simulation model of the system illustrated in Figure 1, where  $r\_no = 2$ . In this case study, there are two normal system operations: an execution packet containing one ALU instruction or two ALU instructions. As can be seen from Figure 2(b), these two operations termed as target operations are notated by the places of 'P1inst' and 'P2inst', respectively. The other places are used to model the operations/functions of the fault-tolerant scheme presented above. We now exploit Figure 2 to explain the modeling methodology and fault-robust verification approach.

Modeling methodology:

- 1. The interconnection description of the functional units; we create a file to describe the interconnection relationship among the functional units.

- 2. Figure 2(a) shows the propagation tables for the functional units, where 'eq' and 'neq' represent 'equal' and 'not equal', respectively.

- 3. Figure 2(b) shows the Petri net graph created to model the system as exhibited in Figure 1. The control signals for target operation 'P1inst' and its associated operations 'Prc1' and 'Prc2' are provided in the control table as displayed in Figure 2(c). For example, when the operation 'P1inst' is executed, the control table is employed to produce the corresponding control signals, such as Sch\_control = '000' and mux\_a = '0', to perform the execution of one ALU instruction with TMR protection. Figure 2(d) gives the conditions for firing the transition from the input place to the output place.

Figure 2. The simulation model of the system illustrated in Figure 1, where r no = 2.

In the following, the target operation 'P1inst' is employed to explain our fault-tolerant verification approach. data flow paths of this operation can be generated by applying the required control signals offered in Figure 2(c), i.e. Sch\_control = '000' and mux\_a = '0'. The procedure of path generation is briefly depicted below (note that the interconnections of the functional units are implicitly

Step 1: The current place in Figure 2 (b) is 'P1inst'. The

applied in the following demonstration of path generation).

- Schedule: Since Sch\_control = '000', according to the propagation table of Schedule, I1\_in1 (data1) is propagated to Sch\_A1\_Out, Sch\_B1\_Out and Sch\_C1\_Out, and I1\_in2 (data2) is propagated to Sch\_A2\_Out, Sch\_B2\_Out and Sch\_C2\_Out.

- ALU: Based on the propagation table of ALU, ALU\_A\_Out, ALU\_B\_Out and ALU\_C\_Out are all equal to 'data1 op data2'.

- Mux: mux\_a = '0', and therefore, 'data1 op data2' is propagated to Mux\_Out1, Mux\_Out2 and Mux\_Out3.

- TMR\_MV: According to the propagation table of TMR\_MV, TMR\_Out is 'data1 op data2' and TMR\_Error is 0.

Step 2: In Step 1, we have collected the data flow paths for the operation 'P1inst'. Then, find out all possible errors which could occur in the data flow paths for 'P1inst' under a selected error model. Here, we adopt the following error model to generate the error patterns that will be used to check the system robustness while 'P1inst' operation is executed.

Error model: To simplify the modeling complexity and reduce the simulation time, we omit the details of the functional units in the system modeling. However, there is no way to inject the faults into the inside of the functional units. Therefore, the errors only can be injected in the outputs of the units. We consider the errors either occurring in a single output port or in the two different output ports.

According to the above error model, we can create the possible errors, which could happen in the data flow paths of the operation 'Plinst'. So, if an error occurs in the 'Plinst' paths and meanwhile the system is executing the operation of 'Plinst', then this error could affect the execution result. For each operation, we can inject the possible errors from the error model into the corresponding data flow paths and investigate whether the detection and recovery schemes built in the system can tolerate the errors or not.

Case 1: A single output port error; an error is injected into the Sch A1 out port as shown in Figure 2(a), propagation table of Schedule unit. As can be seen from Step 1, 'data1' is changed to 'wrong data'. Clearly, the error will be propagated to Mux Out1, then TMR1. So, TMR1 becomes 'wrong data op data2'. In the meantime, TMR2 and TMR3 contain the expression 'data1 op data2'. As a result, TMR Out is 'data1 op data2' and TMR Error is 0. It means that the error can be overcome. Next, there are two output places, 'Prc1' and 'Ptmrs', for input place 'Plinst', where the outcome of TMR Error decides which transition will be enabled. Since TMR\_Error is 0, from Figure 2(d), the transition 'Ttmrs' is fired and the place is transited from 'Plinst' to 'Ptmrs'. There is no more transition when the place is in 'Ptmrs'. Record the result and activate the next error injection.

Case 2: Two output port errors; an error is injected into the Sch\_A1\_out port and the other into Sch\_B1\_out port. Similarly, the errors will be propagated to TMR\_MV inputs, and they are 'wrong\_data1 op data2', 'wrong data2 op data2', and 'data1 op data2', respectively.

Consequently, TMR\_MV fails to produce the correct answer, and sets TMR\_Error is one. Next, the transition 'Ttmrf' is fired and the place 'Prc1' is executed. The operation 'Prc1' is the first error recovery, and if it succeeds, then the transition 'Trc1s' is fired; else, the operation of second recovery 'Prc2' will be activated. Finally, if error recovery succeeds, then the system enters the place 'Prc2s'; else, the system goes into the fail-safe state.

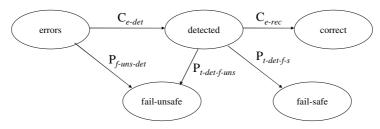

Figure 3 illustrates the complete fault-robust verification process. A platform based on the verification process is developed and used to evaluate the error coverage of the fault-tolerant systems.

Figure 3. The complete fault-robust verification process.

#### SIMULATION RESULTS

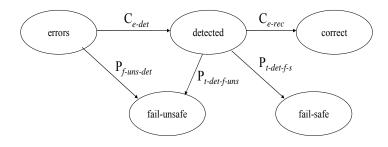

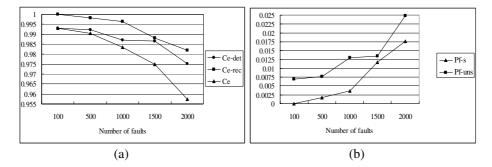

In this section, we use the proposed verification platform to assess the error coverage of system as shown in Figure 1. The design metrics as described below are exploited to justify our approach:

- *Ce*-det: Error-detection coverage, i.e. probability of errors detected;

- *Ce*-*rec*: Error-recovery coverage, i.e. probability of errors recovered given errors detected;

- *Ce* : Error coverage, i.e. probability of errors detected and recovered;

- *P<sub>f</sub> uns* : Probability of system entering the fail-unsafe state;

- $P_{t-\det f s}$ : State transition probability from 'detected' state to 'fail-safe' state.

Table 1 presents the simulation results of the design metrics. The data shown in Model1 are derived from the assumption that the occurring probability is the same for each error in the error model. As shown in [2], the fault/error rate is proportional to the circuit area. Therefore, the occurring probability for the errors located at various functional units should not be identical. The data shown in Model2 take the area effect on the error rate into account. However, the proposed high-level modeling methodology is for the verification purpose of the system robustness. It cannot be used to estimate the area of the functional units. The VHDL design flow is adopted to obtain the area of the units as displayed in Figure 1. To justify the feasibility of our approach and the accuracy of the simulation results, we also conduct the simulation-based fault injection campaigns at RTL level by VHDL design language. Table 2 lists the experimental results.

| Table 1. The | e simulation | results based | l on our method. |

|--------------|--------------|---------------|------------------|

| 10010 1. 11. |              |               |                  |

|        | C <sub>e-det</sub> | C <sub>e-rec</sub> | Ce     | P <sub>t-det-f-s</sub> | P <sub>f-uns</sub> |

|--------|--------------------|--------------------|--------|------------------------|--------------------|

| Model1 | 0.9269             | 0.8710             | 0.8073 | 0.0358                 | 0.1595             |

| Model2 | 0.9971             | 0.9187             | 0.9160 | 0.0390                 | 0.0450             |

| Table 2 | Results | from | simulation-based | 1 approach |

|---------|---------|------|------------------|------------|

|         |         |      |                  |            |

|                            | Faults rate                                 | Ce-det   | Ce-rec   | Ce       | Pt-det-fs | Pf-uns   |

|----------------------------|---------------------------------------------|----------|----------|----------|-----------|----------|

| Workload1                  | w1-1 1 fault:90%<br>2 faults:10%            | 0.999311 | 0.998376 | 0.997688 | 0.001238  | 0.001076 |

| Inst1 : 80%<br>Inst2 : 20% | <b>w1-2</b> 1 fault : 50%<br>2 faults : 50% | 0.999305 | 0.995810 | 0.995118 | 0.003662  | 0.001223 |

|                            | <b>w1-3</b> 1 fault : 10%<br>2 faults : 90% | 0.999217 | 0.993393 | 0.992616 | 0.005986  | 0.001403 |

| Workload2                  | w2-1 1 fault : 90%<br>2 faults : 10%        | 0.999010 | 0.998110 | 0.997122 | 0.001501  | 0.001379 |

| Inst1 : 50%<br>Inst2 : 50% | w2-2 1 fault : 50%<br>2 faults : 50%        | 0.998754 | 0.995374 | 0.994133 | 0.004214  | 0.001658 |

| 11012 . 0070               | <b>w2-3</b> 1 fault : 10%<br>2 faults : 90% | 0.998657 | 0.993268 | 0.991934 | 0.006301  | 0.001673 |

| Workload3                  | <b>w3-1</b> 1 fault : 90%<br>2 faults : 10% | 0.998607 | 0.997900 | 0.996510 | 0.001486  | 0.002006 |

| Inst1 : 20%<br>Inst2 : 80% | <b>w3-2</b> 1 fault : 50%<br>2 faults : 50% | 0.998140 | 0.995215 | 0.993364 | 0.004115  | 0.002529 |

|                            | <b>w3-3</b> 1 fault : 10%<br>2 faults : 90% | 0.997549 | 0.992020 | 0.989588 | 0.007017  | 0.003412 |

Three workloads are developed for the experiments. For fair comparison, three workloads have the various ratios of one and two ALU instructions in an execution packet. According to Table 2, we confirm that the area factor plays an important role in the evaluation of the error coverage. The comparison results between VHDL and our approach with area consideration are summarized as follows (represented by the percentage of the difference):  $-0.17 \sim 0.05\%$  for error-detection coverage,  $-7.24 \sim -6.64\%$  for error-recovery coverage, and  $-7.4 \sim -6.64\%$  for error coverage.

### CONCLUSIONS

A new fault-tolerant verification platform has been proposed to drastically reduce the validation effort and time compared to the previous methodologies. Our fault-tolerant verification platform does not require the detailed hardware implementation, benchmark program development, and fault injection campaigns. However, since our verification approach employs a high level of abstraction to model the fault-robust system, the accuracy of the simulation results will decrease. The preliminary results show that the accuracy of our approach is acceptable, and the verification flow can achieve a rapid dependability assessment. Such a verification flow can significantly decrease the iteration time between different design levels.

#### REFERENCES

- C. Constantinescu, "Impact of Deep Submicron Technology on Dependability of VLSI Circuits," *IEEE Intl. Conf. On Dependable Systems and Networks* (DSN'02), pp. 205-209, 2002.

- [2] P. Shivakumar et al., "Modeling the Effect of Technology Trends on the Soft Error Rate of Combinational Logic," DSN'02, pp. 389-398, 2002.

- [3] T. Karnik, P. Hazucha, and J. Patel, "Characterization of Soft Errors Caused by Single Event Upsets in CMOS Processes," *IEEE Trans. on Dependable and Secure Computing*, Vol. 1, No. 2, pp. 128-143, April-June 2004.

- [4] N. Quach, "High Availability and Reliability in The Itanium Processor," *IEEE Micro*, Vol. 20, issue: 5, pp. 61-69, September-October 2000.

- [5] J. B. Nickle and A. K. Somani, "REESE: A Method of Soft Error Detection in Microprocessors," *DSN'01*, pp. 401-410, 2001.

- [6] S. Mitra et al., "Robust System Design with Built-In Soft-Error Resilience", *IEEE computer*, pp. 43-52, Feb. 2005.

- [7] M. K. Qureshi, O. Mutlu and Y. N. Patt, "Microarchitecture-Based Introspection: A Technique for Transient-Fault Tolerance in Microprocessors", *DSN'05*, pp. 434 – 443, June-July 2005.

- [8] J. Clark and D. Pradhan, "Fault Injection: A Method for Validating Computer-System Dependability," *IEEE Computer*, 28(6), pp. 47-56, June 1995.

- [9] M. C. Hsueh, T. K. Tsai and R. K. Iyer, "Fault Injection Techniques and Tools," *IEEE Computer*, 30(4), pp. 75-82, April 1997.

- [10] C. Constantinescu, "Experimental Evaluation of Error-Detection Mechanisms," *IEEE Trans. on Reliability*, Vol. 52, No. 1, pp. 53-57, March 2003.

- [11] J. Karlsson, P. Liden, P. Dahlgren, R. Johansson and U. Gunneflo, Using Heavy-Ion Radiation to Validate Fault-Handling Mechanisms, *IEEE Micro*, 14(1), Feb. 1994, 8-23.

- [12] G. A. Kanawati, N. A. Kanawati and J. A. Abraham, FERRARI: A Tool for the Validation of System Dependability Properties, *FTCS-22*, 1992, 336-344.

- [13] E. Jenn et al., "Fault Injection into VHDL Models: The MEFISTO Tool," 24<sup>th</sup> IEEE FTCS, pp. 66-75, 1994.

- [14] J. Gracia et al., "Comparison and Application of Different VHDL-Based Fault Injection Techniques," *DFT'01*, pp. 233-241, 2001.

- [15] J. L. Peterson, "Petri Net Theory and the Modeling of System", Prentice-Hall, Inc., Englewood Cliffs, New York (1981).

- [16] Yung-Yuan Chen, Kuen-Long Leu and Chao-Sung Yeh, "Fault-Tolerant VLIW Processor Design and Error Coverage Analysis," The 2006 IFIP International Conference on Embedded and Ubiquitous Computing, pp. 754-765, August 2006.

## **Self-Evaluation of Research Results:**

- The above report summarizes the first-year results accomplished from this three-year research project. It is evident that 99% of the work has been achieved and the preliminary results have been published. The extended versions of the results will be submitted to be considered for journal publication. However, the subjects described in our proposal are big and deserve to be further explored. We definitely achieve the first-year goals set in the proposal.

- We are going to develop a system-level fault-injection tool, which exploits the simulation-based fault injection scheme proposed in this research and can be installed in the CoWare Architect Platform. The tool takes the fault scenario description from the user and then automatically generates the system platform supplemented with the fault injection capability. This kind of fault injection tool can not only facilitate the failure mode and effect analysis (FMEA) and the fault-tolerant validation process, but raise the validation efficiency. The embedded fault-tolerant systems have found fertile ground in intelligent system applications, such as intelligent driver assistance system or intelligent robot system, which require a stringent dependability while the systems are in operation. Since more works depend on the intelligent machines, the reliability issue becomes more important than ever. The fault-tolerant verification platform developed from this research can be applied to the design and analysis of the fault-tolerant systems modeled at high level of abstraction to enhance the overall system dependability. The previous study for the fault injection approach mainly focuses on the VHDL modeling level and rarely discusses the fault injection in system-level design. We want to fulfill this lack.

## Publications associated with this research:

- Kuen-Long Leu, <u>Yung-Yuan Chen</u> and Jwu-E Chen, "A Comparison of Fault Injection Experiments under Different Verification Environments", *IEEE Fourth International Conference on Information Technology & Applications*, pp. 582-587, Jan. 2007. (EI)

- <u>Yung-Yuan Chen</u> and Geng-Wei Wu, "Fault-Tolerant Verification Platform for Systems Modeled at High Level of Abstraction", *I<sup>st</sup> IEEE Systems conference*, pp. 1-7, April 2007. (EI)

- Kun-Jun Chang and <u>Yung-Yuan Chen</u>, "System-Level Fault Injection in SystemC

Design Platform," 8<sup>th</sup> International Symposium on Advanced Intelligent Systems, pp. 354-359, Sept. 2007.

# A Comparison of Fault Injection Experiments under Different Verification Environments

<sup>1</sup>Kuen-Long Leu, <sup>2</sup>Yung-Yuan Chen and <sup>1</sup>Jwu-E Chen

<sup>1</sup>Department of Electrical Engineering National Central University Tao-Yuan, Taiwan E-mail: <u>945401025@cc.ncu.edu.tw</u> jechen@ee.ncu.edu.tw <sup>2</sup>Department of Computer Science and Information Engineering Chung-Hua University Hsin-Chu, Taiwan E-mail: <u>chenyy@chu.edu.tw</u>

Abstract--The main work of this paper is to characterize the dependability of fault-tolerant systems by using two different hardware design environments (SystemC and VHDL). For SystemC, we inject *errors* into the components' outputs, whereas *faults* into the inside of components for VHDL. The difference of the simulation results between SystemC and VHDL is discussed thoroughly through observing two parameters: one is the probability of a fault causing an effective error and another is the relationship between fault duration and error duration. The above two parameters dominate the discrepancy between the two different platforms. The experimental results show the effect of the parameters on the error coverage. This study can promote the fault-tolerant design and verification environment to a higher abstraction level.

*Index Terms*--Error/fault injection, fault-tolerant verification platform, hardware design language, SystemC.

#### I. INTRODUCTION

s system-on-chip (*SoC*) becomes more and more Acomplicated, and contains a large number of transistors, the *SoC* could encounter the reliability problem due to the increased likelihood of faults or radiation-induced soft errors especially when the chip fabrication enters the deep submicron technology [1]-[3]. Thus, it is essential to employ the fault-tolerant techniques in the design of *SoC* to guarantee a high operational reliability in critical applications. Recently, the reliability issue in high-end processors is getting more and more attention [4]-[7]. For example, the Intel Itanium processor provides fault-tolerant features [7], such as enhanced machine check abort (MCA) architecture with extensive error correcting code (ECC), to maximize system reliability and availability.

Generally, there are two kinds of methodologies used to verify the dependability of fault-tolerant systems. One is *physical fault injection* [2] that injects the faults at the IC pin-level, by heavy-ion radiation, by interference with the IC power supplies, or by mutating code and corrupting program state variables. The other is *simulated fault injection* [8]-[10] that uses the simulation to inject faults in simulation model of systems. We can describe the simulation model of systems by hardware description language like VHDL and SystemC. The advantage of simulated fault injection mechanism is that the system dependability can be assessed as early in the design phase, and if necessary to re-design the system, the cost of re-design is reduced significantly.

Recently, the development and verification environment is gradually promoted from RTL to behavioral or system level due to the complexity of *SoC* design. Two popular hardware

description languages, Verilog and VHDL, are not adequate to support the system-level design in more abstract description. The SystemC comes to fill the need of system design [11]-[14]. Because each component developed by SystemC may only contain its behavioral description, the detailed hardware structure is not definite at this level. Therefore, it is impossible to inject a fault into the inside of components. Instead, only the errors can be injected into the components' outputs. The pity is that previous literatures seldom mention the relationship between the fault and error. So designers who want to develop a fault-tolerant system upon higher level of abstraction have no idea about how to link the error scenario to fault scenario. For above reason, this paper wants to propose some practical suggestions to help designers derive more actual simulation results when they are verifying their fault-tolerant systems.

The remaining sections are organized as follows. We briefly introduce the existing error injection methodologies in Section 2 and present ours in Section 3. In Section 4, we discuss and compare the fault injection results derived from the VHDL and SystemC simulation models of a 32-bit fault-tolerant VLIW processor. Finally we propose some valuable conclusions in Section 5 to help derive more accurate experimental results of error simulation at higher abstraction levels.

#### II. RELATED WORK

There are only a few approaches of error injection at high abstraction level based on SystemC. Rothbart et al. [12] inserted fault injection modules (FIM) into the interconnection of the function blocks and fault injection ports (FIP) in the Memory. A fault-injection control unit (FICU) to accomplish the fault simulation at high abstraction level controls the FIM and FIP. Although this methodology will not modify the component description, the FICU will become very complicated if the tested system contains many functional blocks. Fin et al. [13] performed the error injection into SystemC models by presenting a multi-language environment for functional test generation, but they did not observe the behavior of the faulty system. Reference [14] proposed an automated synthesis of single-event upset (SEU) Tolerant architecture based on SystemC environment. Moreover, a tool is provided to allow performing error injecting at behavioral level to validate the SEU tolerant circuits. However, the error injection targets only focus on the storage elements.

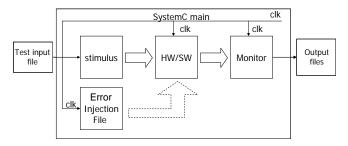

# III. ERROR INJECTION METHODOLOGY IN SYSTEMC

A basic simulation model of SystemC involves three blocks including "Stimulus", "HW/SW" and "Monitor" [11]. The "Stimulus" is responsible for reading the test input file and passing the test patterns at each clock cycle to "HW/SW" which contains the system description and the "Monitor" records systems' outputs. Because all of the three blocks are established upon the C/C++ platform, every signal and input/output port in real hardware can be viewed as a variable in high-level language. If a certain signal is selected to be the fault or error injection target, its value can be altered arbitrarily by declaring its scope as global. According to this principle, we append another block called "Error injection file" to construct our error simulation model as shown in Fig. 1. This file specifies the information for each error injection including the injection time instant, injection target, error type and the error duration. Once the simulation time reaches the injection time of an error, the erroneous value will replace the content of the corresponding port or signal.

Fig. 1: Error simulation model.

#### A. Timing Model of SystemC

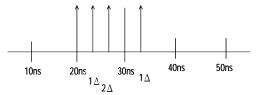

In SystemC, each process will be triggered by certain events. Each event is assigned to a virtual time delay  $\Delta$ .

Fig. 2: Virtual timing model and  $\Delta$  delay of SystemC.

The  $\Delta$  is used to illustrate the relation between cause and effect of real hardware components. As Fig. 2 depicts, there is an event triggered at 20ns, and this event will activate the second event at 20+1 $\Delta$  ns. Then the second event further activates the third event at 20+2 $\Delta$  ns, and so on. Such ripple effect will persist until no more events happen for current iteration.

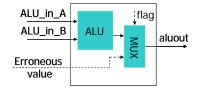

Due to the  $\Delta$  delay, the following situation will result in the error injection fail: Assume an error is injected into an ALU output at 20 ns and this error will be propagated to the next stage at 30 ns. However, ALU is triggered until 20+2 $\Delta$ ns such that the error injected at 20 ns will be overwritten by the new result. Thus, the error injected becomes ineffective. To solve this problem, each component that could be an injection target needs modifying as illustrated in Fig. 3.

Fig. 3: A modified ALU block for error injection.

We declare the 'flag' and 'Erroneous value' in Fig. 3 as global variables so that we can control their values easily. Fig. 4 is an error injection file with flag insertion. Once the simulation time reaches 90 ns, the flag will be set to one, and the multiplexer will choose the erroneous value as the output. The flag will return to zero at 110 ns and at that time the ALU block restores to its normal operation. In this case, the error duration is 20 ns.

```

#include "error_injection_file.h"

#include "system_top.h"

extern systemc_top S1 ;

void Error_in::prc_error_in() {

run_time = sc_simulation_time() ;

switch(run_time) {

case 90 : {

S1.ALU_top_unit->ALU->flag.write(1) ;

S1.ALU_top_unit->ALU->erroneous_value = 1001987144 ;

} break ;

case 110 : {

S1.ALU_top_unit->ALU->flag.write(0) ;

} break ;

}

}

```

Fig. 4: An error injection file example.

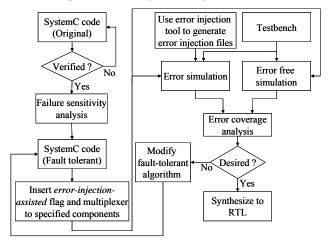

Although this methodology will modify the original component description, the modification is very slight. Furthermore, the insertion of flags and multiplexers can be performed automatically due to its regularity, thus there is no additional burden to designers. In addition, this methodology can apply to not only ALU but also any other functional blocks and storage elements. We have integrated this error injection process into our development and verification framework for the validation of the fault-tolerant systems. We describe the framework next.

B. Development and Verification framework