# 行政院國家科學委員會專題研究計畫 成果報告

# 工作在 GBit 具有低相位雜訊 VCSO 及線性半速率相檢器的時脈回復電路

## 研究成果報告(精簡版)

計畫類別:個別型

計 畫 編 號 : NSC 98-2221-E-216-006-

執 行 期 間 : 98年08月01日至99年07月31日

執 行 單 位 : 中華大學通訊工程學系

計畫主持人: 高曜煌

計畫參與人員:碩士班研究生-兼任助理人員:劉星佑

碩士班研究生-兼任助理人員:盧志良碩士班研究生-兼任助理人員:吳易熾碩士班研究生-兼任助理人員:余柏賢碩士班研究生-兼任助理人員:陳柏綸

大專生-兼任助理人員:戴文嬋 大專生-兼任助理人員:吳鳳庭 大專生-兼任助理人員:汪敬文 大專生-兼任助理人員:呂昆銘 大專生-兼任助理人員:蘇建宇 大專生-兼任助理人員:宋程盛

報告附件:出席國際會議研究心得報告及發表論文

處 理 方 式 : 本計畫涉及專利或其他智慧財產權,2年後可公開查詢

中華民國99年10月20日

# 行政院國家科學委員會補助專題研究計畫成果報告

※工作在 GBit 具有低相位雜訊 VCSO 及線性半速率相檢器的時脈回復電路※

\*\*\*\*\*\*\*\*\*

計畫類別: ●個別型計畫 □整合型計畫

計畫編號: NSC 98-2221-E-216 -006

執行期間: 98年 8月 1日至99年 7月 31日

計畫主持人: 高曜煌教授

共同主持人:

計畫參與人員:吳易熾

執行單位:中華大學通訊工程系

中 華 民 國 99 年 8 月 31 日

# 工作在 GBit 具有低相位雜訊 VCSO 及線性半速率相檢器的時脈回復電路 "A GBit Clock Recovery Circuit with Linear Half Rate Detector and Low Phase Noise VCSO"

計畫編號:NSC 98-2221-E-216 -006

執行期間:98年8月1日至99年7月31日

主持人:高曜煌 中華大學通訊工程系教授

#### 一、中文摘要

本計劃將利用 TSMC 0.18um CMOS 製程 實現一個在 Stratum 3 階層下之 1.244Gb/s 時 脈回復電路並應用於 OC-24 中,主要高速電路 包含振盪器線性半速率相位檢測器及充電 泵,在振盪器設計則採用創新的並具有低相位 雜訊的表面聲波 622MHz 振盪器,它的輸出是 差動的有別於現有的單端輸出,完成一在 OC-24 光纖網路中運行之 1.244Gb/s 時脈資料 回復電路。其中低通濾波器與表面聲波共振腔 為外接於IC,迴路頻寬可彈性調整,初始設計 約在1KHz附近,由於高速運作相位檢測器及 充電泵偏移器將使用電流模邏輯,藉由 MATLAB 與 HSPICE 的閉迴路行為模擬及基 層電晶體電路模擬,本計劃將能成功地將表面 聲波振盪器與時脈回復電路相互結合,預估其 上鎖時間為 1.024ps, 在功率損耗上為 30mW, 頻率微調為 100ppm。

#### 英文摘要

The purpose of this project is to implement a clock and data recovery (CDR) for Stratum 3 application. The bit rate is 1.244GB/s for OC-24 by using TSMC 0.18um CMOS process. Three high speed circuits of voltage controlled SAW Oscillator (VCSO), linear half-rate phase detector, and charge pump are involved. The VCSO with differential outputs is designed for low phase noise application. The low pass loop

filter and SAW resonator are externally connected. The loop bandwidth is initially set around 1KHz. The negative resistance in VCSO is carefully designed to have five times of saw resistance. The tuning is equipped with capacitor bank and varactor. The MATLAB and HSPICE are used for behavior and circuit level simulation, respectively. The VCSO is then combined with CDR for stability and phase lock tests. The target of RMS jitter of retime clock is 1.024ps. The power consumptions are 30mW. And the total tuning range is about 100ppm.

#### 二、簡介

CDR circuits are widely used as timing synchronization in high-speed serial data transfer in SONET, Gigabit Ethernet, and servers. [1-5] Low jitter performance is important for high quality service. SAW filters have been used in clock recover element [1], but is not suitable for non-return to zero (NRZ) data format. CDR is typically used PLL's type. The PLL type CDR will retime the sampling clock first and then re-sampling the input data. In general, VCO provides the most part of jitter. Two types of oscillator are often used for the local clocks. One is the ring oscillator, which has wide tuning but worse jitter performance and is used in the customer side. Most of works utilizes this kind

of VCO for wide band applications. The other is the high stability oscillators using high-Q piezoelectric resonators. Those oscillators have tuning range but better narrower performance and are used in the backbone side. But those operate at low frequency due to the inherent thickness in voltage controlled crystal oscillator (VCXO) or IDT resolution in VCSO. As the transmission rate is raised the low jitter VCO is crucial. VCXO and VCSO are two high stability oscillators. Many kinds of architecture employing high stability oscillators have been presented. [4]

In this study a clock recovery with SAW resonator-based oscillator is examined. The VCO is replaced by VCSO to take advantages of SAW's low jitter and low voltage. 622MHz VCSO is designed for its popular line rate STM-4 or OC-12. Phase detector in high speed operation plays an important part in determining recovered data of CDR. In addition, half rate phase detector is employed to half the VCO rate and save the power [6] As compared to -40dBc/Hz at offset 1KHz [2,3] in ring oscillators, we get ultra-low noise -85dBc/Hz. a low phase noise and low jitter CDR for application to Gigabit Ethernet 1.244GHz is presented.

三、研究方法及成果

#### 電路的細節討論:

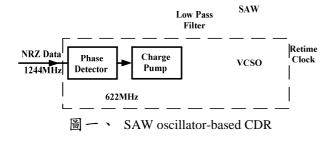

The functional block diagram of PLL-based clock recovery is shown in Fig. 1. Input NRZ data is at 1244MHz and local VCSO is working at 622MHz. Phase comparison is at 622MHz. No digital divider is utilized. Phase detector and charge pump work in high speed and need special care in layout. Elements of low pass filter and SAW resonator outside the dashed box are external connected. The designs are detailed as follows.

#### A. Pierce Oscillator

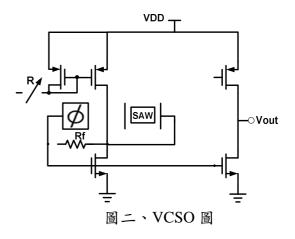

The circuit of VCSO is constructed in Fig. 2. [7] Here, one-port SAW resonator is in pseudo two-port connection. The values of equivalence circuit of SAW is  $L_s = 0.04mH$

;

$$R_s = 15.55\Omega$$

;  $C_s = 1.78 fF$  and  $C_0 = 2.35 pF$  .

Single-stage amplifier with CS configuration is utilized. The loading effect is from the current mirror. Bias current can be adjusted by the external resistor R. According to the Barkhausen's criterion, oscillation starts as the loop gain larger than one and phase shift equal to  $360^{\circ}$ . Except for the single transistor and SAW resonator, additional  $\pi$  phase shift is provided to fulfill the criteria. [8] Output is differential to match the differential input of phase detector. The tuning range of VCSO is about 180ppm.

#### **B.** Phase Detector

The half-rate phase detector shown Fig 3a is designed. Only rising and falling edges are needed, so that it is less affected by signal distortion and has larger jitter tolerance. Another advantage is the half speed in the VCO to save the power [6]. Because random NRZ data has no spectral line in the clock rate, the edge detection is featured to extract out spectral line. The detector contains four Latches L1-L4 and two XORs. As NRZ data through L<sub>1</sub> and L<sub>2</sub> two different pulses at point A and B with width  $\frac{T_{CK}}{2} + \Delta T$  and  $\frac{T_{CK}}{2} - \Delta T$  are generated, respectively, where  $T_{CK}$  is the period of clock and  $\Delta T$  is the time difference of rising edge between data and clock. After XOR, the time difference  $\Delta T$  is obtained. The simulated waveforms are shown in Fig. 3b. The average of  $\Delta T$  is affected by the data transition density so that different pattern may have same difference. To avoid this defect, another reference clock  $V_{ref}$  is generated for error correction.  $L_1$  and  $L_3$ ,  $L_2$  and  $L_4$  can be taken as two complementary triggered Flip-Flop. A half pulse width  $V_{ref}$  is obtained via XOR. As CDR locked, the clock edge is aligned to the center of data pulse, i.e.  $\Delta T$  is equal to  $\frac{T_{CK}}{4}$ . the clock phase is denoted as leading as  $\Delta T < \frac{T_{CK}}{4}$ . On the contrary, the phase is denoted as lag. As for the retime data, retime clock through Flip-Flop formed by  $L_1, L_3, L_2$ , and  $L_4$  is able to sample the input data and after de-multiplexing the data is obtained.

Current mode logic (CML) is employed to realize these high speed logic gates. [9] The swing in CML is small to gain the high speed. M1 and M2 in Fig. 3c act as pre-amplifier in the CML latch to provide enough gain to achieve

fully-swing. Cross-coupled M3 and M4 have loop gain larger than 1 to act as store element. M5 and M6 are switched to select sense or store mode. As clock high, M5 is on, M1and M2 are active. Vout sense the input data. As clock falls to low, M3 and M4 are active and data is latched.

Fig. 3 (a) half-rate PD architecture, (b) Current-mode Latch, (c) simulated half-rate PD waveforms

#### C. Charge Pump and Loop Filter

The current steering charge pump shown in Fig. 4 is used to overcome the high speed operation. [10]  $V_{dif}$  and  $V_{ref}$  are connected to the UP and DN, respectively, to cancel the pattern dependent phase error. Current  $I_{out}$  is fed to the external RC low pass filter. Four nmos are for the input to avoid current mismatch as in conventional nmos and pmos. MP3 and MP4 form a pull-up circuit to speed up the transition in Point A. As UP+ is high, MN2 is on and MN1 is off. Actually, MN1

is not completely switched off and a small still leakage current exists. The weak current  $I_{ss}$  in MN1 is suppressed by current mirror MP1 MP2 charge  $I_{out} = I_{UP} - I_{ss} \approx I_{UP}$ to the output parasitic capacitance. As UP+ transition from high to low, MN2 is switched off and MN1 is turned on such that drain voltage of MP4 is raised to force MP2 off. No extra bias circuit is needed in this so-called current reuse charge pump. The second order loop filter is externally used. The loop bandwidth is set at 1 KHz with  $R_1 = 276\Omega$ ;  $C_1 = 4.33uF$ ;  $C_2 = 224pF$ .

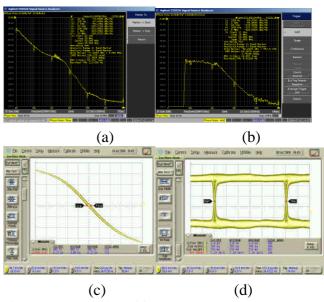

Fig. 4 Zero-offset charge pump,

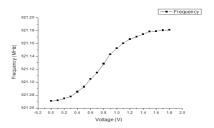

The chip is fabricated by TSMC CMOS 0.18um 2P6M process. Layout of Common-Centroid is specially applied for symmetry. The area is .595\*0.949mm as in Fig. 5 and operating speed is at 1.25GHz NRZ data. The tuning range of VCSO is 180ppm as shown in Fig. 6. The phase noise of SAW oscillator under free running is -163dBc/Hz at offset 1MHz and is -162.5dBc/Hz after locking as in Fig. 7a and 7b, respectively. Obviously, the close-in noise is suppressed under locking. The measured loop bandwidth is around 1 KHz. The measured RMS jitter is 880fs and peak-to-peak jitter is 6.22ps through Agilent 86100c as shown in Fig. 7(c). The locked eye-pattern is also shown in Fig. 7(d). The power consumption is 22.45mW. The performance is summarized in Table I. The comparison also given.The power consumption is 22.45mW. The performance is summarized in Table I. The comparison is also given.

Fig. 5 Die photo of CDR

Fig. 6 VCSO Tuning range 180ppm

Fig. 7 (a) phase noise of free running SAW and (b) phase noise after locking, (c) RMS jitter measurement (d) Eye Pattern.

#### 四、結論

In this study the clock recovery using high-Q SAW resonator is constructed. With the half rate phase detector, the 622MHz saw oscillator by CMOS technology is fabricated. With the high speed design and careful layout, the application is for data speed is at 1244MHz. In the future, the phase shift is embedded into the chip to achieve total integration. The linearity of VCSO is desired to improve.

本計劃的相關研究結果,98 年於 IEEE Trans. EMC 期刊發表一篇論文,並於 2008 APMC 發表會議論文一篇。

| Reference            | [3]             | AD808 [5]  | This Work    |

|----------------------|-----------------|------------|--------------|

| Technology           | CMOS<br>0.18um  | N.A        | CMOS 0.18um  |

| VDD                  | 1.8V            | -5.2V~+5V  | 1.8V         |

| Chip size            | 1.4mm*1.4<br>mm | Package    | 595mm*949mm  |

| Recovery clock       | 625MHz          | 622.08MHz  | 622.08MHz    |

| Data rate            | 1.25Gb/s        | 622.08Mb/s | 1.244Gb/s    |

| Operation range      | 0.95~1.3Gb/s    | 620~624MHz | 622M ± 600Hz |

| Power<br>dissipation | 32mW            | 400mW      | 22mv         |

| RMS Clock Jitter     | 6.66ps          | N.A        | 1.0217ps     |

| Clock Jitter         | 34ps            | N.A        | 7.6ps        |

| Data Jitter          | 12.27ps         | 11.16ps    | 2.8ps        |

| Data Jitter          | 40ps            | N.A        | 17.8ps       |

#### TABLE I SUMMARY OF PERFORMANCE

#### 五、參考文獻

- [1] C.S. Lam, "BAW- and SAW-based Timing Recovery for Frequency Control Applications" *Acoustic Wave for Future Mobile Communication Systems*, March, 2001, Chiba Japan.

- [2] R. Farjad-Rad, C. K. Yang, M. A. Horowitz, and T. H. Lee, "A 0.3-um CMOS 8-Gb/s 4-PAM Serial Link Transceiver", *IEEE J. Solid-State Circuits*, vol. 35, pp. 757-764, 2000.

- [3] C. Y. Yang and J. M. Lin, "A 1.25-Gb/s Burst-Mode Half-Rate Clock and Data Recovery Circuit Using Realigned Oscillation", *IEICE T. Electron.*, vol. E-90-C, pp. 196-200, 2007.

- [4] "10GBit OC-192 Clock & Data Recovery Module", Integrated Circuit Systems, M830/831 Rev 1.0, May 2003, www.icst.com.

- [5] Fiber Optic Receiver with Quantizer and Clock Recovery and Data Retiming, Analog Devices, AD808, 1998, www.analog.com.

- [6] J. Savoj, and B. Razavi, "A 10-Gb/s CMOS Clock and Data Recovery Circuit with a Half-Rate Linear Phase Detector," *IEEE J. Solid-State Circuits*, May 2001.

- [7] M. Furuhata, A. Yajima, K. Goto, H. Sato, T. Funasaka, S. Kawano, S. Fujii, T. Higuchi, and M. Ueno, "Development of Monolithic CMOS-SAW Oscillator" Third International Symposium on Acoustic Wave Devices for Future Mobile Communication Systems, pp.167-170, 2007.

- [8] J. H. Lin and Y. H. Kao, "A Low Phase Noise Voltage Controlled SAW Oscillator With Surface Transverse Wave Resonator for SONET Application" *IEEE Trans. Microw. Theory Tech.*, vol. 55, pp. 60-65, 2007.

- [9] M. M. Green and U. Singh, "Design of CMOS CML circuits for high-speed broadband communications" *Proc. IEEE International Symposium Circuits and Systems*, vol. II, pp. 204-207, May 2003.

- [10] J. H. Esdras and D. S. Alejandro, "A novel CMOS charge-pump circuit with positive feedback for PLL application" *IEEE International Circuits and Systems*, vol.1, pp. 349 -352, Sept 2001.

# 行政院國家科學委員會補助國內專家學者出席國際學術會議報告

2009年12月18日

| 報告人姓     | 生名 | 高曜煌                                                         | 服務機構<br>及職稱 | 中華大學通訊工程系<br>教授       |

|----------|----|-------------------------------------------------------------|-------------|-----------------------|

| 時間       | 間  | 2009/12/7-2009/12/10                                        | 本校核定        | 國科會計畫                 |

| 會議 地點    |    | 新加坡                                                         | 補助字號        | NSC 98-2221-E-216-006 |

| 會議       |    | (中文)2009 IEEE 亞太微波國際學術會議                                    |             |                       |

| 名稱       |    | (英文)2009 IEEE Asia Pacific Microwave Conference (APMC-2009) |             |                       |

| 發表       |    | (中文) 具有 USB 接頭的可攜式高速 HSDPA 網路卡研製                            |             |                       |

| 論文<br>題目 |    |                                                             | B Dongle    |                       |

## 一、簡介

由於無線通信的蓬勃發展,通信速度越來越快,目前已達到毫米波,因此發展微波科技乃是大勢所趨,IEEE意識到此種發展,除了在MTT學術期刊不定期出版專刊外,並在各區域舉辦研討會,亞太地區從1986年在印度首次舉辨亞太微波會議(Asia-Pacific Microwave Conference-APMC)以來,今年是第二十一屆,由國際IEEE微波學會及新加坡分會主辦,行政上由新加坡國立南洋科技大學負責,在SunTec國際會議廳舉行四天,雖然受到金融海嘯及H1N1的影響但仍有來自47個國家超過1000篇論文投稿口頭接受400篇海報張貼300篇,參與非常熱烈。

微波技術開始純粹是爲了應用於雷達、飛彈製導、監察和竊聽等軍事領域,後來則更多的運用於民用系統。正是因爲微波技術的推展,無線電話、遠程遙控、全球定位、無線電廣播、電視和衛星電視直播才能夠得以實現。後來移動電話的出現徹底改變我們的日常生活。由於移動電話帶來的方便是如此的令人印象深刻,公眾對於利用無線技術替換所有有線連接的電腦以及視聽設備的需求日益強烈。實際上,隨著越來越多的電子小發明如藍牙、WiFi、WiMax、ZigBee 以及UWB 等協議的無線通信模塊的模式自動組合,我們正在向這個目標邁進。現下,擁有無線互連的各種各樣的電子電氣設備不斷的裝配我們的辦公室和家庭。除了家裡和辦公室,我們也可以在往返辦公室的路上,或者公共的活動場所,戶外,鄉下,甚至在海上的旅途中,都可以使用網路服務。

大會邀請的主講人爲哈佛大學應用工程与科學院的Federico CAPASSO教授,主題爲Sub-Wavelength Photonics: From Light Manipulation to Quantum Levitation at the Nanoscale

表面電漿極子(Surface Plasmon Polaritons-SPP)允許一個實現集中光中到小於一個波長範圍,從而開闢了新方向,豐富的物理光學和光子學。 利用表面電漿極子再配合先進製造技術(從聚焦離子束,以新的軟光刻技術,使大面積圖案襯底近任意形狀和組成)可觀察從可見光到中紅外線範圍廣泛的現象和應用。此次會談的內容主要有:(一)等離子準直器,這使大

大減少分歧的半導體激光器,帶來令人振奮的機會,梁工程;(二)等離子偏光板任意控制激光偏振;(三)新的光源,如激光等離子天線,能夠創造激烈nanospots的空間分辨化學成像和超高密度光存儲;(四)天線陣列的表面增強拉曼散射;(五)頻率選擇表面啓用一個新的軟光刻技術;(六)有吸引力的和令人反感的光學機械力量與等離子之間的介質波導的子波長的距離。最後,在納米距離內量子受到電磁場所引起的擾動產生的力不可忽視,它會造成卡西米爾吸引和排斥力。此力最近被我們第一次測量到,基於此量子電磁懸浮現象可製造超低摩擦機械元件。

### 二、參加會議經過

本人於 12 月 8 日星期二早上上完大學部電磁學後下午從台北搭乘中華航空到新加坡,出關時己是下午九點,再從机場搭 Shuttle Bus 到市區,並住在 Grand Central Hotel 飯店,距離會場很近,走路約 20 分鐘到會場很方便,亦可搭乘捷運到市府站再步行到會場。由於新加坡採歐美學制此時正值他們的寒假,來台灣旅遊人多,因此机位購買不易,最後被迫購買華夏艙才得以成行,但回程仍被延誤二天,直到星期日才回到台灣。

我於 12 月九日早上註冊,圖一爲會場入口處留影,會議議場有八廳同時進行,早上二場下午兩場每場約五至六篇論文宣讀,時段非常緊湊,我全程參加 RFID 的討論,由於它是今年的重點項目論文篇數較多,而且有很多 RFID 天線方面創新的應用收穫很多。會場中心安排海報及儀器展方便討論及參觀。註冊完後參觀學生競賽海報並與會者討論交換心得,對將來學校研究有幫助。

此大型國際學術會議提供各式各樣的研究成果報告,使與會人士不僅可聆聽各小會場的 口頭報告,亦可至海報會場與學者或其研究生共同討論甚有意思,本來以爲海報展較次等, 來此發現海報展相當受重視,時間長又可面對面溝通非常有效果。

今年我有一篇論文被接受爲口頭官讀,在星期四上午發表,論文題目爲:

# 具有 USB 接頭的可攜式高速 HSDPA 網路卡研製

Fabrication of Portable HSDPA USB Dongle

Authors: Yao-Huang Kao and Huei-Chun Yang

爲一篇先進高頻 2G 及 3.5G 手机傳送高速數據的無了線網卡製造,討論其電磁干擾,

是目前大區域高速無線上網不可或缺的模組,論文重點之一是有關熱散及電磁干擾的探討及解決方案,在此會議中大家討論非常熱烈,由於本文所講的東西是目前各網通廠正在研發, 觀念很新,因此頗受與會學者注意,紛問問題,事後並多方討論,圖二爲筆者報告的情形, 圖三爲作者中午用餐與交大張志揚(左)、中大邱煥凱(右二)及雲科大許孟庭教授(右)合影。

圖一 APMC 會場入口

圖二 口頭報告現場

圖三爲作者中午用餐與交大張志揚(左)、中大邱煥凱(右二)及雲科大許孟庭教授(右)合影

圖四 新加坡烏節路夜景

### 三、參加會議的心得與感想

- 1. 新加坡我已十年沒來過,此次再來覺得他們國際化做得很好,雖然多種族但幾乎以英文爲主,環境看來很西式,兩所國立大學很國際化提供大額獎學金吸引世界各地优秀學生及教授,台灣的光電專家林清隆教授即被他們延聘至南洋大學電机學院。

- 2. 新加坡快速發展,辦理技術及投資移民人口由三百萬擴增至四百萬,但由於規劃得當市容顯得井井有條,一般公寓蓋 20 層,地上一層透空,使視野廣擴,並闢停車位,住宅區不設賣場,所以景觀很整潔,賣場則集中在地鐵站附近,人們一般以地鐵及 Bus 爲主要交通工具,圖四爲作者於會後在最熱鬧的鳥節路散步,可看見各百貨公司張燈結綵熱鬧非凡,耶誕氣氛濃厚。

- 3.亞太微波會議由區域性的集會演變成世界微波領域的三大頂級會議之一。因此,亞太 微波會議在生產和服務領域的技術、非技術方面,越來越受到專業技術人員以及專業培養訓 練人員的歡迎。會議的參加者包括微波和毫米波通信領域的教授,軟硬體工程師和研究生。 他們從事的工作包括天線、合成材料、配件、設備、測量儀器、消費產品、軟體等的研究、 設計、生產、安裝維護以及應用。除了這些參加者之外,亞太微波會議也有政府部門,工業 界人士,金融家以及其他方面的專家參加。時至今日,亞太微波會議已經成爲一個服務於包 括應用電磁學的學術領域、微波軟硬體生產的工業領域、以及電信服務領域在內的獨特的世 界一流的國際會議。

- 4. 由於手機的推出以及後續的無線互連系統的發展已引發的一場工業的微型技術革命。這些通信系統製造消費產品不但是一個勞動密集型的工作,也是資金密集型和技術密集型,爲了支援這些改變,新加坡也成立類似工研院的 Astar 研究院以帶動大學及企業,活躍在微波技術的基礎研究與應用領域方面。

- 5. 因爲新加坡位於歐亞地區的中心,有地理優勢,此次參加人數超過 1000 人,是新加坡舉辦的最大規模的國際微波盛會。

#### 四、攜回資料

最後,感謝學校及國科會的輔助得以成行,討論此先進科技,由於環保僅攜回大會光碟一片,有興趣同仁歡迎借閱。我的電話為 5186036, Email:yhkao@chu.edu.tw。

## 無研發成果推廣資料

## 98年度專題研究計畫研究成果彙整表

計畫編號: 98-2221-E-216-006-計畫主持人:高曜煌

技術移轉

(外國籍)

參與計畫人力 博士生

權利金

碩士生

博士後研究員

專任助理

計畫名稱:工作在 GBit 具有低相位雜訊 VCSO 及線性半速率相檢器的時脈回復電路 備註(質化說 量化 明:如數個計畫 本計畫實 共同成果、成果 實際已達成 際貢獻百 預期總達成 單位 成果項目 列為該期刊之 數(被接受 數(含實際已 分比 達成數) 封面故事... 或已發表) 等) 0 100% 期刊論文 0 100% 篇 研究報告/技術報告 論文著作 0 0 100% 研討會論文 100% 專書 0 0 申請中件數 100% 專利 件 0 0 100% 已獲得件數 國內 0 0 100% 件 件數 技術移轉 0 0 權利金 100% 千元 0 0 100% 碩士生 參與計畫人力 博士生 0 0 100% 人次 (本國籍) 0 0 博士後研究員 100% 0 0 100% 專任助理 2 0 100% 期刊論文 0 0 100% 篇 研究報告/技術報告 論文著作 3 0 50% 研討會論文 0 0 專書 100% 章/本 0 0 100% 申請中件數 專利 件 0 0 已獲得件數 100% 國外 0 0 件數 100% 件

0

0

0

0

0

0

0

0

100%

100%

100%

100%

100%

千元

人次

兩篇國際學術論文在頂尖 IEEE 電磁干擾期刊及在日本應用物理發表.

|    | 成果項目            | 量化 | 名稱或內容性質簡述 |

|----|-----------------|----|-----------|

| 科  | 測驗工具(含質性與量性)    | 0  |           |

| 教  | 課程/模組           | 0  |           |

| 處  | 電腦及網路系統或工具      | 0  |           |

| 計  | 教材              | 0  |           |

| 畫加 | 舉辦之活動/競賽        | 0  |           |

|    | 研討會/工作坊         | 0  |           |

| 項  | 電子報、網站          | 0  |           |

| 目  | 計畫成果推廣之參與(閱聽)人數 | 0  |           |

# 國科會補助專題研究計畫成果報告自評表

請就研究內容與原計畫相符程度、達成預期目標情況、研究成果之學術或應用價值(簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性)、是否適合在學術期刊發表或申請專利、主要發現或其他有關價值等,作一綜合評估。

| 1. | . 請就研究內容與原計畫相符程度、達成預期目標情況作一綜合評估             |

|----|---------------------------------------------|

|    | ■達成目標                                       |

|    | □未達成目標(請說明,以100字為限)                         |

|    | □實驗失敗                                       |

|    | □因故實驗中斷                                     |

|    | □其他原因                                       |

|    | 說明:                                         |

| 2. | . 研究成果在學術期刊發表或申請專利等情形:                      |

|    | 論文:■已發表 □未發表之文稿 □撰寫中 □無                     |

|    | 專利:□已獲得 □申請中 ■無                             |

|    | 技轉:□已技轉 □洽談中 ■無                             |

|    | 其他:(以100字為限)                                |

|    | 在亞太微波會議已發表(2009)目前亦有寫成更完整論文準備投稿中.           |

| 3. | . 請依學術成就、技術創新、社會影響等方面,評估研究成果之學術或應用價         |

|    | 值(簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性)(以           |

|    | 500 字為限)                                    |

|    | 本論文有下列三種影響                                  |

|    | 1. 應用於高速GBit光通訊的時脈回復電路與SAW元件結合提供最穩信號源對將來電端計 |

|    | 算所需穩定信號源可提供應用                               |

|    | 2. 結合鎖相迴路可提供高速 Jitter Reduction 的應用具有商用的价值. |

|    | 3. 製作的 CMOS IC 中採用立體電感可縮小 IC 面積是一種新的創舉.     |